JTAG/UART/SPI/Diagnostic I/O used in Sony repair centers if a PS3 couldn't be fixed by software.

Notes:

Service Connectors

Preproduction Generation

| Used on |

Type of Connector

|

| MPU-501 (CEB-2040) |

CN6504: Headerpins

CN6507: ZIF Connector

|

CN6504 (SC_JTAG)

| Pin |

Pogo-Pin Con. |

Name |

Connected to |

Function |

Group

|

| 1 |

NO |

? |

? |

?

|

| 2 |

NO |

? |

? |

?

|

| 3 |

NO |

? |

? |

?

|

| 4 |

NO |

? |

? |

?

|

| 5 |

NO |

? |

? |

?

|

| 6 |

NO |

? |

? |

?

|

| 7 |

NO |

? |

? |

?

|

| 8 |

NO |

? |

? |

?

|

| 9 |

NO |

? |

? |

?

|

| 10 |

NO |

? |

? |

?

|

| 11 |

NO |

? |

? |

?

|

| 12 |

NO |

? |

? |

?

|

| 13 |

NO |

? |

? |

?

|

| 14 |

NO |

? |

? |

?

|

| 15 |

NO |

? |

? |

?

|

| 16 |

NO |

? |

? |

?

|

| 17 |

NO |

? |

? |

?

|

| 18 |

NO |

? |

? |

?

|

| 19 |

NO |

? |

? |

?

|

| 20 |

NO |

? |

? |

?

|

CN6507 (STATUS)

| Pin |

Pogo-Pin Con. |

Name |

Connected to |

Function |

Group

|

| 1 |

NO |

? |

? |

?

|

| 2 |

NO |

? |

? |

?

|

| 3 |

NO |

? |

? |

?

|

| 4 |

NO |

? |

? |

?

|

| 5 |

NO |

? |

? |

?

|

| 6 |

NO |

? |

? |

?

|

| 7 |

NO |

? |

? |

?

|

| 8 |

NO |

? |

? |

?

|

| 9 |

NO |

? |

? |

?

|

CN6504 (SC_JTAG) (DECR)

| Pin |

Pogo-Pin Con. |

Name |

Connected to |

Function |

Group

|

| 1 |

NO |

GND |

DC-DC Regulator |

Ground line |

-

|

| 2 |

?? |

SC_RESET/RST |

Syscon |

System Reset |

Syscon JTAG

|

| 3 |

NO |

+3.3V_EVER |

DC-DC Regulator |

+3.3V line |

-

|

| 4 |

?? |

JRTCK |

Syscon |

Return Test Clock |

Syscon JTAG

|

| 5 |

?? |

JTCK |

Syscon |

Test Clock

|

| 6 |

?? |

JTMS |

Syscon |

Test Mode Select

|

| 7 |

?? |

JTDO |

Syscon |

Test Data Out

|

| 8 |

?? |

JTDI |

Syscon |

Test Data In

|

| 9 |

?? |

JNTRST |

Syscon |

Test Reset

|

| 10 |

NO |

+3.3V_EVER |

DC-DC Regulator |

+3.3V line |

-

|

- (SC) RESET is connected to S6503 Button

Diag/Backup (DECR)

| Pin |

Pogo-Pin Con. |

Name |

Connected to |

Function |

Group

|

| - |

?? |

Backup Mode? |

SysCon |

Backup Mode? |

Syscon Modes

|

| - |

?? |

Diag Mode? |

SysCon |

Diagnose Mode?

|

- Backup is Connected to S6502-1 Switch

- Diag is Connected to S6502-2 Switch

SC_UART (DECR)

| Pin |

Pogo-Pin Con. |

Name |

Connected to |

Function |

Standby Voltage |

Group

|

| - |

?? |

+3.3V_EVER? |

DC-DC Regulator |

+3.3V line? |

3.3 |

-

|

| - |

?? |

Rx? |

Syscon |

Receive UART? |

0 |

Syscon UART

|

| - |

?? |

Tx? |

Syscon |

Transfer UART? |

3.14

|

| - |

?? |

GND? |

DC-DC Regulator |

Ground line |

0 |

-

|

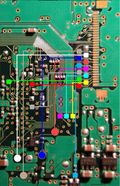

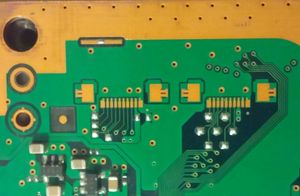

Pictures (Traces from DECR)

1st Generation

CN4009

First Generation Connector as seen on

COK-002

First Generation Connector as seen on

COK-001

First Generation Connector as seen on

COOKIE-13

| Pin |

Pogo-Pin Con. |

Name |

Connected to |

Function |

Group

|

| 1 |

NO |

+5V_EVER |

DC-DC Regulator |

+5V line |

-

|

| 2 |

YES |

TRST |

Syscon |

Test Reset (nTRST) |

Syscon JTAG

|

| 3 |

YES |

TDI |

Syscon |

Test Data In

|

| 4 |

YES |

RTCK |

Syscon |

Return Test Clock

|

| 5 |

YES |

TCK |

Syscon |

Test Clock

|

| 6 |

YES |

TDO |

Syscon |

Test Data Out

|

| 7 |

YES |

TMS |

Syscon |

Test Mode Select

|

| 8 |

YES |

SC_RESET |

Syscon |

System Reset (nSRST)

|

| 9 |

NO |

GND |

DC-DC Regulator |

Ground line |

-

|

| 10 |

YES |

RxD |

Syscon |

Serial Receive |

Syscon UART

|

| 11 |

YES |

TxD |

Syscon |

Serial Transmit

|

| 12 |

NO |

GND |

DC-DC Regulator |

Ground line |

-

|

| 13 |

YES |

Diag Mode |

Syscon |

Diagnose Mode |

Syscon Modes

|

| 14 |

YES |

Backup Mode |

Syscon |

Backup Mode

|

| 15 |

NO |

+3.3V_EVER |

DC-DC Regulator |

+3.3V line |

-

|

| 16 |

YES |

NC |

- |

-

|

| 17 |

NO |

RMC |

Syscon |

Reset MechaCon or TestMode |

Syscon Modes

|

| 18 |

NO |

SB_TxD |

South Bridge |

Serial Transmit |

South Bridge UART

|

| 19 |

NO |

SB_RxD |

South Bridge |

Serial Receive

|

| 20 |

NO |

SW_4_A |

(W)LAN |

Power Switch |

LAN & WLAN

|

| 21 |

NO |

BE_TRG_OUT |

CELL BE |

Trigger Out |

Component Tests

|

| 22 |

NO |

RSX_TRG_OUT |

RSX |

Trigger Out

|

| 23 |

NO |

SB_TRG_OUT |

South Bridge |

Trigger Out

|

| 24 |

NO |

BE_CHKSTP_OUT |

CELL BE |

Checkstop Out

|

| 25 |

NO |

RSX_CHKSTP_OUT |

RSX |

Checkstop Out

|

| 26 |

NO |

SB_CHKSTP_OUT |

South Bridge |

Checkstop Out

|

| 27 |

NO |

+1.2V_MC_VDDIO |

DC-DC Regulator |

+1.2V line |

-

|

| 28 |

NO |

+1.5V_RSX_VDDIO |

DC-DC Regulator |

+1.5V line

|

| 29 |

NO |

GND |

DC-DC Regulator |

Ground line

|

| 30 |

NO |

+5V_EVER |

DC-DC Regulator |

+5V line

|

It looks like Kayocera 6240

CELL_BE JTAG Testpads

| Pin |

Pogo-Pin Con. |

Name |

Connected to |

Function |

Group

|

| CL1103 |

YES |

TDO |

pin AW14 @ CELL BE |

Test Data Out |

CELL BE JTAG

|

| CL1104 |

YES |

TDI |

pin AW13 @ CELL BE |

Test Data In

|

| CL1105 |

YES |

TCK |

pin BA13 @ CELL BE |

Test Clock

|

| CL1106 |

YES |

TMS |

pin AW12 @ CELL BE |

Test Mode Select

|

| CL1107 |

YES |

/TRST |

pin AV14 @ CELL BE |

Test Reset (nTRST)

|

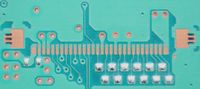

2nd Generation

Second Generation Connector as seen on DIA-001

CN4003

| Pin |

Pogo-Pin Con. |

Name |

Connected to |

Function |

Group

|

| 10 |

YES |

SC_TXD |

SysCon |

Serial Transmit |

Syscon UART

|

| 9 |

YES |

SC_RXD |

SysCon |

Serial Receive

|

| 8 |

NO |

RMC |

SysCon |

Reset MechaCon OR TestMode |

Syscon Modes

|

| 7 |

YES |

Diag Mode |

SysCon |

Diagnose Mode

|

| 6 |

YES |

Backup Mode |

SysCon |

Backup Mode

|

| 5 |

NO |

SB_SIO0_RXD_M |

South Bridge |

Serial Receive |

South Bridge UART

|

| 4 |

NO |

SB_SIO0_TXD_M |

South Bridge |

Serial Transmit

|

| 3 |

NO |

SW_4_B |

USB |

Power Switch |

USB

|

| 2 |

NO |

+5V_EVER |

DC-DC Regulator |

+5V line |

-

|

| 1 |

NO |

GND |

DC-DC Regulator |

Ground line

|

CN4004

| Pin |

Pogo-Pin Con. |

Name |

Connected to |

Function |

Group

|

| 10 |

YES |

TRST |

SysCon |

Test Reset (nTRST) |

Syscon JTAG

|

| 9 |

YES |

TDI |

SysCon |

Test Data In

|

| 8 |

YES |

RTCK |

SysCon |

Return Test Clock

|

| 7 |

YES |

TCK |

SysCon |

Test Clock

|

| 6 |

YES |

TDO |

SysCon |

Test Data Out

|

| 5 |

YES |

TMS |

SysCon |

Test Mode Select

|

| 4 |

YES |

SC_RESET |

SysCon |

System Reset (nSRST)

|

| 3 |

NO |

+3.3V_EVER |

DC-DC Regulator |

+3.3V line |

-

|

| 2 |

NO |

GND |

DC-DC Regulator |

Ground line

|

| 1 |

NO |

GND |

DC-DC Regulator |

Ground line

|

Second Generation Connector as seen on SEM-001

CN1001 (CELL_BE_JTAG)

| Pin |

Pogo-Pin Con. |

Name |

Connected to |

Function |

Group

|

| 12 |

NO |

GND |

DC-DC Regulator |

Ground line

|

| 11 |

NO |

+1.2V_MC2_VDDIO |

DC-DC Regulator |

+1.2V Line

|

| 10 |

NO |

GND |

DC-DC Regulator |

Ground line

|

| 9 |

NO |

BE_POWGOOD |

CELL BE |

Power Good

|

| 8 |

NO |

BE_RESET |

CELL BE |

Cell Reset

|

| 7 |

NO |

/BE_CHKSTP_OUT |

CELL BE |

Cell Checkstop Out

|

| 6 |

NO |

/BE_RESET_AND |

CELL BE |

Cell Reset?

|

| 5 |

NO |

BE_TDO |

CELL BE |

Test Data Out

|

| 4 |

NO |

BE_TMS |

CELL BE |

Test Mode Select

|

| 3 |

NO |

BE_TCK |

CELL BE |

Test Clock

|

| 2 |

NO |

BE_TRST |

CELL BE |

Test Reset (nTRST)

|

| 1 |

NO |

BE_TDI |

CELL BE |

Test Data In

|

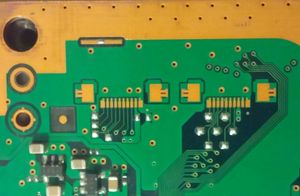

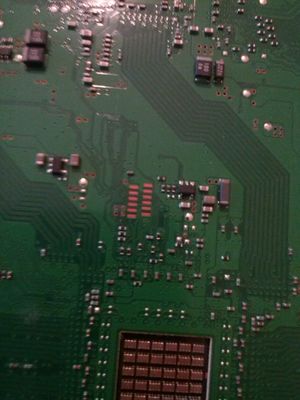

3rd Generation

Third Generation Service Connector as seen on VER-001

Third Generation Service Connector as seen on DYN-001

Third Generation Service Connector as seen on DYN-001

Third Generation Service Connector as seen on SURTEES-03

CN???? v1

| Pin |

Pogo-Pin Con. |

Name |

Connected to |

Function |

Group

|

| 14 |

NO |

SB_PIO14? |

South Bridge |

? |

?

|

| 13 |

YES |

TOOL1 |

SysCon |

Clock output for tool |

Syscon JTAG

|

| 12 |

YES |

"P65" |

SysCon |

(GPIO) |

Syscon Modes?

|

| 11 |

YES |

SC_RxD |

SysCon |

Serial Receive |

Syscon UART

|

| 10 |

YES |

SC_TxD |

SysCon |

Serial Transmit

|

| 9 |

NO |

RESET |

SysCon |

Reset |

Syscon JTAG (throught 3 missing SMD components. See lines 7,8,9 disconnected: 1 and 2)

|

| 8 |

NO |

FLMD0 |

SysCon |

Flash programming mode

|

| 7 |

NO |

TOOL0 |

SysCon |

Data input/output for tool

|

| 6 |

NO |

SB_PIO15? |

South Bridge |

? |

?

|

| 5 |

NO |

SB_SIO0_RXD_M |

South Bridge |

Serial Receive |

South Bridge UART

|

| 4 |

NO |

SB_SIO0_TXD_M |

South Bridge |

Serial Transmit

|

| 3 |

NO |

"P73" |

SysCon |

(GPIO) |

Syscon Modes?

|

| 2 |

NO |

GND |

DC-DC Regulator |

Ground Line |

-

|

| 1 |

NO |

+5V_EVER |

DC-DC Regulator |

+5V Line

|

CN???? v2

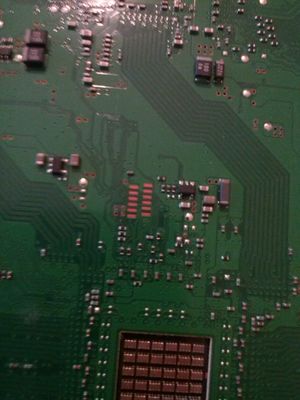

Since JSD-001 there are some notable changes in the circuit design, the syscon was moved to the opposite side of the motherboard, the location of this service connector was moved very close to syscon. Pins 7,8,9 of this service connector had added an (unpopulated from factory) unknown SMD component (i guess resistors or diodes). Pins 10,11,12,13 of this service connector are not connected to syscon anymore, it seems was repurposed and connected to a different unknown component (southbridge ?)

Third Generation Service Connector as seen on JSD-001

Third Generation Service Connector as seen on MPX-001

https://web.archive.org/web/20160309151818/ http://pastie.org/private/h8osu80ksjr0xdta97zida

https://pastebin.com/hp3Uz6F7 (mirror)

http://docs-asia.electrocomponents.com/webdocs/14a3/0900766b814a341b.pdf

|

This article is marked for rewrite/restructuring in proper wiki format.

You can help PS3 Developer wiki by editing it. |