K4Y50164UC-JCB3

Jump to navigation

Jump to search

Samsung K4Y50164UC-JCB3[edit | edit source]

(CECHAxx/COK-001, CECHBxx/COK-001, CECHCxx/COK-002, CECHExx/COK-002W)

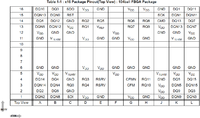

Datasheet: Samsung K4Y50164UC-JCB3

| Manufacturer | DRAM | DRAM type | Density | Organization | Banks | Interface | Revision | Package type | Power & Temp. | Speed |

|---|---|---|---|---|---|---|---|---|---|---|

| K: Samsung | 4: DRAM | J: GDDR3 SDRAM Y: XDR DRAM G: GDDR5 SDRAM |

10: 1G, 8K/32ms 50: 512M, 32K/16ms 52: 512M, 8K/32ms 12: ? |

16: x16bit 32: x32bit |

4: 8 Banks 5: 16 Banks |

U: DRSL, 1.8V, 1.2V Q: SSTL-2 1.8V, 1.8V K: ? T: ? F: POD_15(1.5V,1.5V) |

C: 4th Gen. E: 6th Gen. G: 8th Gen. I: 10th Gen. J: 11th Gen. |

J: BOC (Lead-free) S: ? K: ? H (GDDR5): FBGA-170 |

C: Normal Power (0ºC–95ºC) | B3 (XDR): 3.2Gbps, 35ns, 20Cycles 14 (GDDR3): 1.4ns (700MHz) 15 (GDDR5): 1.5ns (667MHz) |

| This article is marked for rewrite/restructuring in proper wiki format. You can help PS3 Developer wiki by editing it. |

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||