RAM: Difference between revisions

Jump to navigation

Jump to search

| (41 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

= | = System Memory (RAM) = | ||

The PS3 has | == Chipnumers @ SKU's == | ||

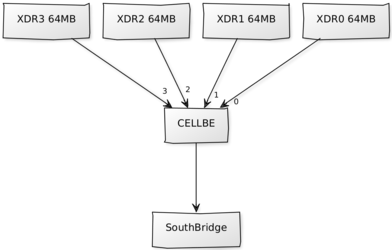

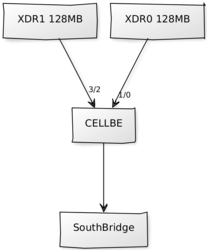

<div style="float:right">[[File:XDR-quad to CELLBE to SouthBridge diagram.png|x250px|thumb|left|XDR-quad to CELLBE to SouthBridge diagram of PS3 FAT and early PS3 Slim's CECH-20..A/DYN-001]][[File:XDR-dual to CELLBE to SouthBridge diagram.png|x250px|thumb|right|XDR-dual to CELLBE to SouthBridge diagram since CECH-21..A/SUR-001]]<br />[[File:X5116AC-3C-E.jpg|200px|thumb|right|XDR-quad memory<br />[[CECHGxx]] / [[SEM-00x|SEM-001]]]]</div> | |||

The PS3 has a [https://en.wikipedia.org/wiki/Differential_signalling differential signalling] 64 bit bus with 256MB of [https://en.wikipedia.org/wiki/XDR_DRAM Rambus XDR DRAM] main system memory. Older models use four 64MB chips, while newer models uses two 128MB chips. | |||

{|class="wikitable" style="line-height:1.2em; font-size:1em" | |||

|- | |||

|- | ! PS3 Model !! Mobo Model !! RAM Serial !! Amount !! Notes | ||

|- | |||

| [[CECHAxx]]<br>[[CECHBxx]] || [[COK-001]] || [[X5116ACSE-3C-E]]<br /> or<br />[[K4Y50164UC-JCB3 ]] || style="text-align:center;" | 4*16bits || | |||

|- | |||

| [[CECHCxx]]<br>[[CECHExx]] || [[COK-002]] || [[X5116ACSE-3C-E]]<br /> or<br />[[K4Y50164UC-JCB3 ]] || style="text-align:center;" | 4*16bits || | |||

|- | |||

| [[CECHGxx]] || [[SEM-001]] || [[X5116ACSE-3C-E]] || style="text-align:center;" | 4*16bits || | |||

|- | |||

| [[CECHHxx]] || [[DIA-001]] || [[X5116ADSE-3C-E]] || style="text-align:center;" | 4*16bits || | |||

|- | |||

| [[CECHJxx]]<br>[[CECHKxx]] || [[DIA-002]] || [[K4Y50164UE-JCB3]] || style="text-align:center;" | 4*16bits || | |||

|- | |||

| [[CECHLxx]] || [[VER-001]] || [[X5116ADSE-3C-E]]<br /> or<br />[[IDRD51-0-A1F1C-32C]] || style="text-align:center;" | 4*16bits || | |||

|- | |||

| [[CECHMxx]] || [[VER-001]] || [[X5116ADSE-3C-E]] || style="text-align:center;" | 4*16bits || | |||

|- | |||

| [[CECHPxx]] || [[VER-001]] || [[X5116ADSE-3C-E]] || style="text-align:center;" | 4*16bits || | |||

|- | |||

| [[CECHQxx]] || [[VER-001]] || [[X5116ADSE-3C-E]] || style="text-align:center;" | 4*16bits || | |||

|- | |||

| [[CECH-20xx]] || [[DYN-001]] || [[X5116ADSE-3C-E]] || style="text-align:center;" | 4*16bits || | |||

|- | |||

| colspan="5" style="padding:0px" | | |||

|- | |||

| [[CECH-21xx]] || [[SUR-001]] || [[X1032BASE-3C-F]] || style="text-align:center;" | 2*32bits || | |||

|- | |||

| [[CECH-25xx]] || [[JTP-001]] || [[X1032BASE-3C-F#Elpida X1032BASE-3CA2-F|X1032BASE-3CA2-F ]] || style="text-align:center;" | 2*32bits || | |||

|- | |||

| [[CECH-25xx]] || [[JSD-001]] || [[X1032BASE-3C-F]] || style="text-align:center;" | 2*32bits || | |||

|- | |||

| [[CECH-30xx]] || [[KTE-001]] || [[X1032BASE-3C-F]] || style="text-align:center;" | 2*32bits || | |||

|- | |||

| colspan="5" style="padding:0px" | | |||

|- | |||

| [[CECH-40xx]] || [[MSX-001]] || [[X1032BBBG-3C-F]] || style="text-align:center;" | 2*32bits || | |||

|- | |||

| [[CECH-40xx]] || [[MPX-001]] || [[X1032BBBG-3C-F]] || style="text-align:center;" | 2*32bits || | |||

|- | |- | ||

| | | [[CECH-42xx]] || [[NPX-001]] || [[X1032BBBG-3C-F]] || style="text-align:center;" | 2*32bits || | ||

|- | |- | ||

| | | [[CECH-42xx]] || [[PPX-001]] || || style="text-align:center;" | 2*32bits || | ||

|- | |- | ||

| | | [[CECH-42xx]] || [[PQX-001]] || [[X1032BBBG-3C-F]] || style="text-align:center;" | 2*32bits || | ||

|- | |- | ||

| | | colspan="5" style="padding:0px" | | ||

|- | |- | ||

| | | [[CECH-43xx]] || [[RTX-001]] || || style="text-align:center;" | 2*32bits || | ||

|- | |- | ||

| [[CECH-43xx]] || [[REX-001]] || [[K4Y12324TE-KCB3]] || style="text-align:center;" | 2*32bits || | |||

|} | |} | ||

<gallery> | |||

File:Elpida XDR DRAM on production at June 4, 2013.jpg|Elpida XDR DRAM on production at June 4, 2013 | |||

File:Elpida XDR DRAM out of production at June 4, 2013.jpg|Elpida XDR DRAM out of production at June 4, 2013 | |||

</gallery> | |||

=== Alternate table === | |||

=== | |||

{| border="1" cellspacing="0" cellpadding="5" border="#999" class="wikitable" style="border:1px solid #999; border-collapse: collapse;" | {| border="1" cellspacing="0" cellpadding="5" border="#999" class="wikitable" style="border:1px solid #999; border-collapse: collapse;" | ||

|- bgcolor="#cccccc" | |- bgcolor="#cccccc" | ||

! Type !! Size !! Speed !! Voltage !! Packaging !! | ! Type !! Size !! Speed !! Voltage !! Packaging !! Manufact. !! Serial Number !! Amount !! Models | ||

|- | |||

| Rambus XDR || 64MB || 400MHz || 1.8V+/-0.09V || FBGA-104 || Elpida || [[X5116ACSE-3C-E]] || 4x || [[CECHAxx]]/[[COK-00x#COK-001|COK-001]] up to including [[CECHGxx]]/[[SEM-00x|SEM-001]] | |||

|- | |||

| Rambus XDR || 64MB || 400MHz || 1.8V+/-0.09V || FBGA-104 || Samsung || [[K4Y50164UC-JCB3]] || 4x || ?Some initial models? | |||

|- | |||

| Rambus XDR || 64MB || 400MHz || 1.8V+/-0.09V || FBGA-100 || Samsung || [[K4Y50164UE-JCB3]] || 4x || [[CECHJxx]]/[[DIA-00x#DIA-002|DIA-002]] and [[CECHKxx]]/[[DIA-00x#DIA-002|DIA-002]] | |||

|- | |||

| Rambus XDR || 64MB || 400MHz || 1.8V+/-0.09V || FBGA-104 || Elpida || [[X5116ADSE-3C-E]] || 4x || [[CECHHxx]]/[[DIA-00x#DIA-001|DIA-001]], [[CECHLxx]]/[[VER-00x|VER-001]] up and including [[CECHQxx]]/[[VER-00x|VER-001]] and PS3 Slim [[CECH-20xx]]/[[DYN-00x|DYN-001]] | |||

|- | |- | ||

| | | Rambus XDR || 64MB || 400MHz || 1.8V+/-0.09V || FBGA-104 || Qimonda || [[IDRD51-0-A1F1C-32C]] || 4x || reported on some [[CECHLxx]]/[[VER-00x|VER-001]] | ||

|- | |- | ||

| | | Rambus XDR || 128MB || 400MHz || 1.5V+/-0.075V || FBGA-150 || Elpida || [[X1032BASE-3C-F]] || 2x || [[CECH-21xx]]/[[SUR-00x|SUR-001]] and newer | ||

|- | |- | ||

|} | |} | ||

=== | == Other XDR Rambus references == | ||

* [https://www-01.ibm.com/chips/techlib/techlib.nsf/techdocs/AF7832F379790768872572D10047E52B/$file/CellBE_HIG_65nm_v1.01_8Jun2007.pdf CellBE_HIG_65nm_v1.01_8Jun2007.pdf] | |||

* [http://www.capsl.udel.edu/~jmanzano/Cell/docs/arch/BE_Hardwar_Init_Guide_v1.3_31March2006.pdf BE_Hardwar_Init_Guide_v1.3_31March2006.pdf] | |||

* [http://www.rambus.com/assets/documents/products/dl_0362_v0_71.pdf Rambus XDR IO Cell (XIO) - dl_0362_v0_71.pdf] | |||

* [http://www.rambus.com/assets/documents/products/dl_0161_v0_8.pdf XDR Architecture - Rambus dl_0161_v0_8.pdf] | |||

* [http://www.rambus.com/assets/documents/products/xdr_dl_0476.pdf 8x4Mx16/8/4/2 - Rambus xdr_dl_0476.pdf] | |||

* [http://www.rambus.com/assets/documents/products/dl_0169l_v0_81.pdf XDR Clock Generator - Rambus dl_0169l_v0_81.pdf] | |||

* dl_0178_v0_93.pdf (january 2006) | |||

* dl_0178_v0_95.pdf (august 2006) | |||

* http://www.mirrorcreator.com/files/1KD96OYT/xdr_product_guide_mar_06_0.pdf_links | |||

* http://www.mirrorcreator.com/files/1C1NTTYD/Elpida_E1819E20_0.pdf_links | |||

* http://www.mirrorcreator.com/files/KGNOVWHK/Elpida_E0881E20_0.pdf_links | |||

* http://www.mirrorcreator.com/files/SSF2GNEK/Samsung_k4y50xx4ue_rev10.pdf_links | |||

* http://www.mirrorcreator.com/files/1FQRE8S5/Samsung_k4y50xx4uc_rev11_0.pdf_links | |||

* http://www.mirrorcreator.com/files/11S5L1EW/Elpida_E1033E40_EOL_0.pdf_links | |||

= Video Memory (VRAM) = | |||

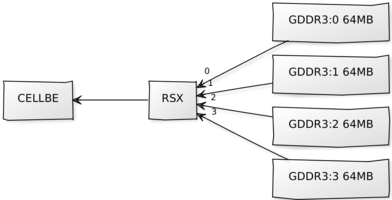

<div style="float:right">[[File:GDDR3 to RSX to CellBE diagram.png|x200px|thumb|right|Quad 64MB GDDR3 (256MB total) to RSX to CellBE diagram ]][[File:RSX_MEMORY.jpg|200px|thumb|left|RSX bare die<br />GPU in centre<br />4x GDDR3]]</div> | |||

<div style="float:right">[[File: | |||

The 256MB of GDDR3 memory is located inside the [[RSX]] chip using four 64MB FBGA chips. | |||

{| border="1" cellspacing="0" cellpadding="5" border="#999" class="wikitable" style="border:1px solid #999; border-collapse: collapse;" | {| border="1" cellspacing="0" cellpadding="5" border="#999" class="wikitable" style="border:1px solid #999; border-collapse: collapse;" | ||

|- bgcolor="#cccccc" | |- bgcolor="#cccccc" | ||

! Type !! Size !! Speed !! Voltage !! Packaging !! Manufacturer !! Serial Number !! Description | ! Type !! Size !! Speed !! Voltage !! Packaging !! Manufacturer !! Serial Number !! Description | ||

|- | |- | ||

| | | GDDR3 || 64MB (512Mbit) || 700MHz || 2.0V +/-0.1V || <strike>FBGA-136</strike> on-die || Samsung || [[K4J52324QC-SC14]] || 256MB total (4 chips) for PS3 Graphics Memory | ||

|- | |||

| GDDR3 || 64MB (512Mbit) || 700MHz || 2.0V +/-0.1V || <strike>FBGA-136</strike> on-die || Infineon/Qimonda || [[HYB18H512322AF-14]] || 256MB total (4 chips) for PS3 Graphics Memory | |||

|- | |||

| GDDR3 || 64MB (512Mbit) || ? || ? || ? || Samsung || [[K4J52324KI-JC14]] || 256MB total (4 chips) for PS3 Graphics Memory | |||

|- | |||

| GDDR3 || 64MB (512Mbit) || ? || ? || ? || Samsung || [[K4J52324KJ-JC14]] || 256MB total (4 chips) for PS3 Graphics Memory | |||

|- | |||

| GDDR3 || 128MB (1024Mbit) ? || ? || ? || ? || Hynix || [[H5RS5223DFA]] || 256MB total (2 chips ?) for PS3 Graphics Memory | |||

|- | |- | ||

|} | |} | ||

: | |||

= PS2 Compatibility Memory = | |||

[https://en.wikipedia.org/wiki/RDRAM Rambus RDRAM]<br> | |||

See: [[PS2 Compatibility]] | |||

{{Motherboard Components}}<noinclude>[[Category:Main]]</noinclude> | |||

Latest revision as of 15:12, 2 August 2022

System Memory (RAM)[edit | edit source]

Chipnumers @ SKU's[edit | edit source]

The PS3 has a differential signalling 64 bit bus with 256MB of Rambus XDR DRAM main system memory. Older models use four 64MB chips, while newer models uses two 128MB chips.

| PS3 Model | Mobo Model | RAM Serial | Amount | Notes |

|---|---|---|---|---|

| CECHAxx CECHBxx |

COK-001 | X5116ACSE-3C-E or K4Y50164UC-JCB3 |

4*16bits | |

| CECHCxx CECHExx |

COK-002 | X5116ACSE-3C-E or K4Y50164UC-JCB3 |

4*16bits | |

| CECHGxx | SEM-001 | X5116ACSE-3C-E | 4*16bits | |

| CECHHxx | DIA-001 | X5116ADSE-3C-E | 4*16bits | |

| CECHJxx CECHKxx |

DIA-002 | K4Y50164UE-JCB3 | 4*16bits | |

| CECHLxx | VER-001 | X5116ADSE-3C-E or IDRD51-0-A1F1C-32C |

4*16bits | |

| CECHMxx | VER-001 | X5116ADSE-3C-E | 4*16bits | |

| CECHPxx | VER-001 | X5116ADSE-3C-E | 4*16bits | |

| CECHQxx | VER-001 | X5116ADSE-3C-E | 4*16bits | |

| CECH-20xx | DYN-001 | X5116ADSE-3C-E | 4*16bits | |

| CECH-21xx | SUR-001 | X1032BASE-3C-F | 2*32bits | |

| CECH-25xx | JTP-001 | X1032BASE-3CA2-F | 2*32bits | |

| CECH-25xx | JSD-001 | X1032BASE-3C-F | 2*32bits | |

| CECH-30xx | KTE-001 | X1032BASE-3C-F | 2*32bits | |

| CECH-40xx | MSX-001 | X1032BBBG-3C-F | 2*32bits | |

| CECH-40xx | MPX-001 | X1032BBBG-3C-F | 2*32bits | |

| CECH-42xx | NPX-001 | X1032BBBG-3C-F | 2*32bits | |

| CECH-42xx | PPX-001 | 2*32bits | ||

| CECH-42xx | PQX-001 | X1032BBBG-3C-F | 2*32bits | |

| CECH-43xx | RTX-001 | 2*32bits | ||

| CECH-43xx | REX-001 | K4Y12324TE-KCB3 | 2*32bits | |

Alternate table[edit | edit source]

| Type | Size | Speed | Voltage | Packaging | Manufact. | Serial Number | Amount | Models |

|---|---|---|---|---|---|---|---|---|

| Rambus XDR | 64MB | 400MHz | 1.8V+/-0.09V | FBGA-104 | Elpida | X5116ACSE-3C-E | 4x | CECHAxx/COK-001 up to including CECHGxx/SEM-001 |

| Rambus XDR | 64MB | 400MHz | 1.8V+/-0.09V | FBGA-104 | Samsung | K4Y50164UC-JCB3 | 4x | ?Some initial models? |

| Rambus XDR | 64MB | 400MHz | 1.8V+/-0.09V | FBGA-100 | Samsung | K4Y50164UE-JCB3 | 4x | CECHJxx/DIA-002 and CECHKxx/DIA-002 |

| Rambus XDR | 64MB | 400MHz | 1.8V+/-0.09V | FBGA-104 | Elpida | X5116ADSE-3C-E | 4x | CECHHxx/DIA-001, CECHLxx/VER-001 up and including CECHQxx/VER-001 and PS3 Slim CECH-20xx/DYN-001 |

| Rambus XDR | 64MB | 400MHz | 1.8V+/-0.09V | FBGA-104 | Qimonda | IDRD51-0-A1F1C-32C | 4x | reported on some CECHLxx/VER-001 |

| Rambus XDR | 128MB | 400MHz | 1.5V+/-0.075V | FBGA-150 | Elpida | X1032BASE-3C-F | 2x | CECH-21xx/SUR-001 and newer |

Other XDR Rambus references[edit | edit source]

- CellBE_HIG_65nm_v1.01_8Jun2007.pdf

- BE_Hardwar_Init_Guide_v1.3_31March2006.pdf

- Rambus XDR IO Cell (XIO) - dl_0362_v0_71.pdf

- XDR Architecture - Rambus dl_0161_v0_8.pdf

- 8x4Mx16/8/4/2 - Rambus xdr_dl_0476.pdf

- XDR Clock Generator - Rambus dl_0169l_v0_81.pdf

- dl_0178_v0_93.pdf (january 2006)

- dl_0178_v0_95.pdf (august 2006)

- http://www.mirrorcreator.com/files/1KD96OYT/xdr_product_guide_mar_06_0.pdf_links

- http://www.mirrorcreator.com/files/1C1NTTYD/Elpida_E1819E20_0.pdf_links

- http://www.mirrorcreator.com/files/KGNOVWHK/Elpida_E0881E20_0.pdf_links

- http://www.mirrorcreator.com/files/SSF2GNEK/Samsung_k4y50xx4ue_rev10.pdf_links

- http://www.mirrorcreator.com/files/1FQRE8S5/Samsung_k4y50xx4uc_rev11_0.pdf_links

- http://www.mirrorcreator.com/files/11S5L1EW/Elpida_E1033E40_EOL_0.pdf_links

Video Memory (VRAM)[edit | edit source]

The 256MB of GDDR3 memory is located inside the RSX chip using four 64MB FBGA chips.

| Type | Size | Speed | Voltage | Packaging | Manufacturer | Serial Number | Description |

|---|---|---|---|---|---|---|---|

| GDDR3 | 64MB (512Mbit) | 700MHz | 2.0V +/-0.1V | Samsung | K4J52324QC-SC14 | 256MB total (4 chips) for PS3 Graphics Memory | |

| GDDR3 | 64MB (512Mbit) | 700MHz | 2.0V +/-0.1V | Infineon/Qimonda | HYB18H512322AF-14 | 256MB total (4 chips) for PS3 Graphics Memory | |

| GDDR3 | 64MB (512Mbit) | ? | ? | ? | Samsung | K4J52324KI-JC14 | 256MB total (4 chips) for PS3 Graphics Memory |

| GDDR3 | 64MB (512Mbit) | ? | ? | ? | Samsung | K4J52324KJ-JC14 | 256MB total (4 chips) for PS3 Graphics Memory |

| GDDR3 | 128MB (1024Mbit) ? | ? | ? | ? | Hynix | H5RS5223DFA | 256MB total (2 chips ?) for PS3 Graphics Memory |

PS2 Compatibility Memory[edit | edit source]

Rambus RDRAM

See: PS2 Compatibility

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||