USB: Difference between revisions

Jump to navigation

Jump to search

m (Removed protection from "USB") |

m (Text replacement - "!important!important" to "!important") |

||

| (16 intermediate revisions by 4 users not shown) | |||

| Line 1: | Line 1: | ||

= USB 2.0 = | |||

<div style="float:right">[[File:CECHC GL852- IC3305.JPG|200px|thumb|left|GL852 USB-Hub as seen on [[CECHCxx]]]]</div> | <div style="float:right">[[File:CECHC GL852- IC3305.JPG|200px|thumb|left|[[GL852]] USB-Hub 64-pin as seen on [[CECHCxx]]]]</div> | ||

Depending on the [[SKU Models]] the PS3 is equiped with 6x (Tool/DECR), 4 or 2 [http://en.wikipedia.org/wiki/USB USB (Universal Serial Bus)] 2.0 ports with maximum bandwidth of 480 Mbit/s (~57 MB/s), connected internally to a USB-Hub chip. | |||

'''Note:''' On PS3 Slim [[CECH-20xx]]/[[DYN-00x|DYN-001]] and later, the USB port datalines are directly connected to [[South Bridge]] without a USB-Hub chip (port is initialised via DC switch IC connected to [[South Bridge]] and TH3301 thermistor protect 5V input). | |||

For more detailed info about the USB hub pinout see: [[GL852]] | |||

<gallery> | <gallery> | ||

File:DYN-001 USB lines (top view).jpg|USB lines top view (common traces for all slim models) | File:DYN-001 USB lines (top view).jpg|USB lines top view (common traces for all slim models) | ||

File:DYN-001USB lines (bottom view).jpg|USB lines bottom view (common traces for all slim models) | File:DYN-001USB lines (bottom view).jpg|USB lines bottom view (common traces for all slim models) | ||

File:JSD-001 and JTP-001 USB connector TH3301 thermistor and DC switch IC to southbridge v2.jpg|[[JSD-001]]/[[JTP-001]] [[USB]] connector [[Protection|TH3301 thermistor]] and DC switch IC to [[South Bridge]] | |||

</gallery> | </gallery> | ||

| Line 16: | Line 17: | ||

{| border="1" cellspacing="0" cellpadding="5" border="#999" class="wikitable" style="border:1px solid #999; border-collapse: collapse;" | {| border="1" cellspacing="0" cellpadding="5" border="#999" class="wikitable" style="border:1px solid #999; border-collapse: collapse;" | ||

|+ USB 1.x/2.0 standard pinout | |||

|- bgcolor="#cccccc" | |- bgcolor="#cccccc" | ||

! Pin !! Signal !! Description | ! Pin !! Color !! Signal !! Description | ||

|- | |- | ||

| | | Shell || {{NA}} || Shield || Metal housing | ||

|- | |- | ||

| | | 1 || style="color:white; background-color:#CC3333;" | Red || V<sub>BUS</sub> || Power / +5 volt DC (max.500mA) | ||

|- | |- | ||

| | | 2 || style="color:black!important; background-color:white;" | White || D- || rowspan="2" | USB 2.0 differential pair | ||

|- | |- | ||

| | | 3 || style="color:white; background-color:#33CC33;" | Green || D+ | ||

|- | |||

| 4 || style="color:white; background-color:#333333;" | Black || GND || Ground | |||

|- | |- | ||

|} | |} | ||

{| border="1" cellspacing="0" cellpadding="5" border="#999" class="wikitable" style="border:1px solid #999; border-collapse: collapse;" | |||

|+ USB 1.x/2.0 mini/micro pinout | |||

{| border="1" cellspacing="0" cellpadding="5" border="#999" class="wikitable | |||

|- bgcolor="#cccccc" | |- bgcolor="#cccccc" | ||

! Pin | ! Pin !! Color !! Signal !! Description | ||

|- | |- | ||

| | | Shell || {{NA}} || Shield || Metal housing | ||

|- | |- | ||

| | | 1 || style="color:white; background-color:#CC3333;" | Red || V<sub>BUS</sub> || Power | ||

|- | |- | ||

| | | 2 || style="color:black!important; background-color:white;" | White || D- || rowspan="2" | USB 2.0 differential pair | ||

|- | |- | ||

| | | 3 || style="color:white; background-color:#33CC33;" | Green || D+ | ||

|- | |- | ||

| | | 4 || {{NA}} || ID || Permits detection of which end of a cable is plugged in:<br/>• "A" connector (host): connected to the signal ground<br>• "B" connector (device): not connected | ||

|- | |- | ||

| | | 5 || style="color:white; background-color:#333333;" | Black || GND || Ground | ||

|- | |- | ||

| | |}'''Note:''' used on many [[Peripherals]] for charging/sync | ||

[[ | |||

[[Category: | {{Motherboard Components}}<noinclude>[[Category:Main]]</noinclude> | ||

Latest revision as of 05:16, 1 July 2023

USB 2.0[edit | edit source]

Depending on the SKU Models the PS3 is equiped with 6x (Tool/DECR), 4 or 2 USB (Universal Serial Bus) 2.0 ports with maximum bandwidth of 480 Mbit/s (~57 MB/s), connected internally to a USB-Hub chip.

Note: On PS3 Slim CECH-20xx/DYN-001 and later, the USB port datalines are directly connected to South Bridge without a USB-Hub chip (port is initialised via DC switch IC connected to South Bridge and TH3301 thermistor protect 5V input).

For more detailed info about the USB hub pinout see: GL852

JSD-001/JTP-001 USB connector TH3301 thermistor and DC switch IC to South Bridge

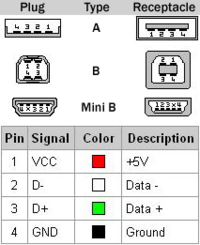

Generic USB Pinout[edit | edit source]

| Pin | Color | Signal | Description |

|---|---|---|---|

| Shell | N / A | Shield | Metal housing |

| 1 | Red | VBUS | Power / +5 volt DC (max.500mA) |

| 2 | White | D- | USB 2.0 differential pair |

| 3 | Green | D+ | |

| 4 | Black | GND | Ground |

| Pin | Color | Signal | Description |

|---|---|---|---|

| Shell | N / A | Shield | Metal housing |

| 1 | Red | VBUS | Power |

| 2 | White | D- | USB 2.0 differential pair |

| 3 | Green | D+ | |

| 4 | N / A | ID | Permits detection of which end of a cable is plugged in: • "A" connector (host): connected to the signal ground • "B" connector (device): not connected |

| 5 | Black | GND | Ground |

Note: used on many Peripherals for charging/sync

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||