CXD4302GB-1: Difference between revisions

Jump to navigation

Jump to search

| Line 6: | Line 6: | ||

Seen in early NAND FAT: [[CECHAxx]]/[[COK-00x#COK-001|COK-001]] and [[CECHBxx]]/[[COK-00x#COK-001|COK-001]] <br /><br /><br /><br /><br /><br /> | Seen in early NAND FAT: [[CECHAxx]]/[[COK-00x#COK-001|COK-001]] and [[CECHBxx]]/[[COK-00x#COK-001|COK-001]] <br /><br /><br /><br /><br /><br /> | ||

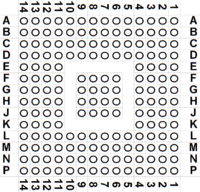

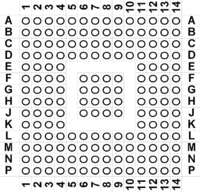

<div style="float:right">[[File:CXD4302GB-GRID-bw-ss2-bottomside.png|200px|thumb|left|IC3801 (StarShip 2)<br />BALL-GRID-ARRAY overview<br />IC view, facing BGA<br />A1 marker:northeast/topright]]<br />[[File:CXD4302GB-GRID-bw-pcbview.png|200px|thumb|left|IC3801 (StarShip 2)<br />BALL-GRID-ARRAY overview<br />PCB view, facing BGA<br />A1 marker:northwest/topleft]]</div> | <div style="float:right">[[File:CXD4302GB-GRID-bw-ss2-bottomside.png|200px|thumb|left|IC3801 (StarShip 2)<br />BALL-GRID-ARRAY overview<br />IC view, facing BGA<br />A1 marker:northeast/topright]]<br />[[File:CXD4302GB-GRID-bw-pcbview.png|200px|thumb|left|IC3801 (StarShip 2)<br />BALL-GRID-ARRAY overview<br />PCB view, facing BGA<br />A1 marker:northwest/topleft]]</div> | ||

{| border="1" cellspacing="0" cellpadding="5" border="#999" class="wikitable sortable" style="border:1px solid #999; border-collapse: collapse;" | {| border="1" cellspacing="0" cellpadding="5" border="#999" class="wikitable sortable" style="border:1px solid #999; border-collapse: collapse;" | ||

| Line 14: | Line 13: | ||

! Pad # !! Name !! Description | ! Pad # !! Name !! Description | ||

|- | |- | ||

| A1 || HA[0] || /SB_EBUS_ADDR0 | | A1 || HA[0] || /SB_EBUS_ADDR0 (via JL9338 [[EBUS]]) | ||

|- | |- | ||

| A2 || XHOE || /SB_EBU_OE (via JL9305 [[EBUS]]) | | A2 || XHOE || /SB_EBU_OE (via JL9305 [[EBUS]]) | ||

|- | |- | ||

| A3 || HA[2] || /SB_EBUS_ADDR2 | | A3 || HA[2] || /SB_EBUS_ADDR2 (via JL9336 [[EBUS]]) | ||

|- | |- | ||

| A4 || HA[4] || /SB_EBUS_ADDR4 | | A4 || HA[4] || /SB_EBUS_ADDR4 (via JL9334 [[EBUS]]) | ||

|- | |- | ||

| A5 || HA[6] || /SB_EBUS_ADDR6 | | A5 || HA[6] || /SB_EBUS_ADDR6 (via JL9332 [[EBUS]]) | ||

|- | |- | ||

| A6 || HA[17] || /SB_EBUS_ADDR17 | | A6 || HA[17] || /SB_EBUS_ADDR17 (via JL9321 [[EBUS]]) | ||

|- | |- | ||

| A7 || XHWE || /SB_EBUS_SWE (via JL9304 [[EBUS]] | | A7 || XHWE || /SB_EBUS_SWE (via JL9304 [[EBUS]] | ||

|- | |- | ||

| A8 || HA[9] || /SB_EBUS_ADDR9 | | A8 || HA[9] || /SB_EBUS_ADDR9 (via JL9329 [[EBUS]]) | ||

|- | |- | ||

| A9 || HA[11] || /SB_EBUS_ADDR11 | | A9 || HA[11] || /SB_EBUS_ADDR11 (via JL9327 [[EBUS]]) | ||

|- | |- | ||

| A10 || VDD33 || | | A10 || VDD33 || | ||

|- | |- | ||

| A11 || HA[14] || /SB_EBUS_ADDR14 | | A11 || HA[14] || /SB_EBUS_ADDR14 (via JL9324 [[EBUS]]) | ||

|- | |- | ||

| A12 || HA[16] || /SB_EBUS_ADDR16 | | A12 || HA[16] || /SB_EBUS_ADDR16 (via JL9322 [[EBUS]]) | ||

|- | |- | ||

| A13 || BSTCLK || JL9302 | | A13 || BSTCLK || /SB_EBUS_SYSCLK with R3806 0 Ohm inline (via JL9302 [[EBUS]]) | ||

|- | |- | ||

| A14 || IA[3] || | | A14 || IA[3] || | ||

| Line 47: | Line 46: | ||

! Pad # !! Name !! Description | ! Pad # !! Name !! Description | ||

|- | |- | ||

| B1 || XHCE0 || | | B1 || XHCE0 || /SB_EBUS_CE0 (via JL9307 [[EBUS]]) | ||

|- | |- | ||

| B2 || HA[1] || /SB_EBUS_ADDR1 | | B2 || HA[1] || /SB_EBUS_ADDR1 (via JL9337 [[EBUS]]) | ||

|- | |- | ||

| B3 || HA[3] || /SB_EBUS_ADDR3 | | B3 || HA[3] || /SB_EBUS_ADDR3 (via JL9335 [[EBUS]]) | ||

|- | |- | ||

| B4 || HA[5] || /SB_EBUS_ADDR5 | | B4 || HA[5] || /SB_EBUS_ADDR5 (via JL9333 [[EBUS]]) | ||

|- | |- | ||

| B5 || | | B5 || HA[7] || /SB_EBUS_ADDR7 (via JL9331 [[EBUS]]) | ||

|- | |- | ||

| B6 || | | B6 || XHRST || (C3827 100pF CH 50V & R3801 10kOhm) to /SB_EBUS_RESET (with R3838 0 Ohm inline) + /SS2_RESET (with R3839 0 Ohm inline) | ||

|- | |- | ||

| B7 || | | B7 || HA[8] || /SB_EBUS_ADDR8 (via JL9330 [[EBUS]]) | ||

|- | |- | ||

| B8 || | | B8 || HA[10] || /SB_EBUS_ADDR10 (via JL9328 [[EBUS]]) | ||

|- | |- | ||

| B9 || | | B9 || HA[12] || /SB_EBUS_ADDR12 (via JL9326 [[EBUS]]) | ||

|- | |- | ||

| B10 || | | B10 || HA[13] || /SB_EBUS_ADDR13 (via JL9325 [[EBUS]]) | ||

|- | |- | ||

| B11 || | | B11 || HA[15] || /SB_EBUS_ADDR15 (via JL9323 [[EBUS]]) | ||

|- | |- | ||

| B12 || | | B12 || XHBE || /SB_EBUS_IOR (via JL9303 [[EBUS]]) | ||

|- | |- | ||

| B13 || | | B13 || IA[2] || | ||

|- | |- | ||

| B14 || VDD33 || | | B14 || VDD33 || | ||

| Line 433: | Line 432: | ||

|} | |} | ||

''remark: the following Pad #letter's are not used: I, O, Q, S, X, Z, AI, AO, AQ, AS, AX, AZ'' | ''remark: the following Pad #letter's are not used: I, O, Q, S, X, Z, AI, AO, AQ, AS, AX, AZ'' | ||

{{Motherboard Components}}<noinclude>[[Category:Main]]</noinclude> | {{Motherboard Components}}<noinclude>[[Category:Main]]</noinclude> | ||

Revision as of 13:13, 6 August 2014

Sony CXD4302GB-1 / CXD4302GB-T6 (Starship 2)

alt.part no.: CXD4302GB-T6

8-753-265-45 / IC3801

Seen in early NAND FAT: CECHAxx/COK-001 and CECHBxx/COK-001

| A | ||

|---|---|---|

| Pad # | Name | Description |

| A1 | HA[0] | /SB_EBUS_ADDR0 (via JL9338 EBUS) |

| A2 | XHOE | /SB_EBU_OE (via JL9305 EBUS) |

| A3 | HA[2] | /SB_EBUS_ADDR2 (via JL9336 EBUS) |

| A4 | HA[4] | /SB_EBUS_ADDR4 (via JL9334 EBUS) |

| A5 | HA[6] | /SB_EBUS_ADDR6 (via JL9332 EBUS) |

| A6 | HA[17] | /SB_EBUS_ADDR17 (via JL9321 EBUS) |

| A7 | XHWE | /SB_EBUS_SWE (via JL9304 EBUS |

| A8 | HA[9] | /SB_EBUS_ADDR9 (via JL9329 EBUS) |

| A9 | HA[11] | /SB_EBUS_ADDR11 (via JL9327 EBUS) |

| A10 | VDD33 | |

| A11 | HA[14] | /SB_EBUS_ADDR14 (via JL9324 EBUS) |

| A12 | HA[16] | /SB_EBUS_ADDR16 (via JL9322 EBUS) |

| A13 | BSTCLK | /SB_EBUS_SYSCLK with R3806 0 Ohm inline (via JL9302 EBUS) |

| A14 | IA[3] | |

| B | ||

| Pad # | Name | Description |

| B1 | XHCE0 | /SB_EBUS_CE0 (via JL9307 EBUS) |

| B2 | HA[1] | /SB_EBUS_ADDR1 (via JL9337 EBUS) |

| B3 | HA[3] | /SB_EBUS_ADDR3 (via JL9335 EBUS) |

| B4 | HA[5] | /SB_EBUS_ADDR5 (via JL9333 EBUS) |

| B5 | HA[7] | /SB_EBUS_ADDR7 (via JL9331 EBUS) |

| B6 | XHRST | (C3827 100pF CH 50V & R3801 10kOhm) to /SB_EBUS_RESET (with R3838 0 Ohm inline) + /SS2_RESET (with R3839 0 Ohm inline) |

| B7 | HA[8] | /SB_EBUS_ADDR8 (via JL9330 EBUS) |

| B8 | HA[10] | /SB_EBUS_ADDR10 (via JL9328 EBUS) |

| B9 | HA[12] | /SB_EBUS_ADDR12 (via JL9326 EBUS) |

| B10 | HA[13] | /SB_EBUS_ADDR13 (via JL9325 EBUS) |

| B11 | HA[15] | /SB_EBUS_ADDR15 (via JL9323 EBUS) |

| B12 | XHBE | /SB_EBUS_IOR (via JL9303 EBUS) |

| B13 | IA[2] | |

| B14 | VDD33 | |

| C | ||

| Pad # | Name | Description |

| C1 | HRDY | /SB_EBUS_ACK (via JL9308 EBUS) |

| C2 | XHCE1 | /SB_EBUS_CE2 (via JL9306 EBUS) |

| C3 | HD[2] | /SB_EBUS_DATA2 |

| C4 | HD[3] | /SB_EBUS_DATA3 |

| C5 | ||

| C6 | ||

| C7 | ||

| C8 | ||

| C9 | ||

| C10 | ||

| C11 | ||

| C12 | ||

| C13 | ||

| C14 | ||

| D | ||

| Pad # | Name | Description |

| D1 | BRDY | R38002 22 Ohm inline and R3807 10KOhm pullup to /SS2_BRDY (via JL9309 EBUS) |

| D2 | XINT | R3808 10KOhm pullup to /SS2_INT (via JL9310 EBUS) |

| D3 | HD[10] | |

| D4 | GND | Ground |

| D5 | VDD33 | |

| D6 | VDD33 | |

| D7 | ||

| D8 | ||

| D9 | VDD33 | |

| D10 | VDD33 | |

| D11 | ||

| D12 | ||

| D13 | ||

| D14 | ||

| E | ||

| Pad # | Name | Description |

| E1 | VDD33 | |

| E2 | HD[8] | /SB_EBUS_DATA8 |

| E3 | HD[1] | /SB_EBUS_DATA1 |

| E4 | HD[9] | /SB_EBUS_DATA9 |

| E11 | ||

| E12 | ||

| E13 | ||

| E14 | ||

| F | ||

| Pad # | Name | Description |

| F1 | ||

| F2 | PLLSEL[3] | to VDD33 |

| F3 | PLLSEL[1] | to VDD33 |

| F4 | HD[0] | /SB_EBUS_DATA0 |

| F6 | GND | Ground |

| F7 | GND | Ground |

| F8 | GND | Ground |

| F9 | GND | Ground |

| F11 | ||

| F12 | ||

| F13 | ||

| F14 | ||

| G | ||

| Pad # | Name | Description |

| G1 | ||

| G2 | ||

| G3 | ||

| G4 | ||

| G6 | GND | Ground |

| G7 | GND | Ground |

| G8 | GND | Ground |

| G9 | GND | Ground |

| G11 | ||

| G12 | VDD33 | |

| G13 | ||

| G14 | ||

| H | ||

| Pad # | Name | Description |

| H1 | ||

| H2 | GNDP | Ground |

| H3 | ||

| H4 | VDD33 | |

| H6 | GND | Ground |

| H7 | GND | Ground |

| H8 | GND | Ground |

| H9 | GND | Ground |

| H11 | VDD33 | |

| H12 | ||

| H13 | ||

| H14 | ||

| J | ||

| Pad # | Name | Description |

| J1 | ||

| J2 | VDD33 | |

| J3 | ||

| J4 | PLLEN | via R3844 0 Ohm to VDD33 |

| J6 | GND | Ground |

| J7 | GND | Ground |

| J8 | GND | Ground |

| J9 | GND | Ground |

| J11 | ||

| J12 | ||

| J13 | ||

| J14 | ||

| K | ||

| Pad # | Name | Description |

| K1 | XIN | via R3842 0 Ohm to VDD33 |

| K2 | GND | Ground |

| K3 | ||

| K4 | ||

| K11 | VDD33 | |

| K12 | ||

| K13 | ||

| K14 | ||

| L | ||

| Pad # | Name | Description |

| L1 | ||

| L2 | ||

| L3 | ||

| L4 | GND | Ground |

| L5 | ||

| L6 | VDD33 | |

| L7 | VDD33 | |

| L8 | ||

| L9 | ||

| L10 | VDD33 | |

| L11 | GND | Ground |

| L12 | ||

| L13 | ||

| L14 | XEXPOR | via R3846 0 Ohm to VDD33 |

| M | ||

| Pad # | Name | Description |

| M1 | ||

| M2 | ||

| M3 | ||

| M4 | ||

| M5 | ||

| M6 | ||

| M7 | ||

| M8 | ||

| M9 | ||

| M10 | ||

| M11 | ||

| M12 | VDD33 | |

| M13 | ||

| M14 | ||

| N | ||

| Pad # | Name | Description |

| N1 | ||

| N2 | ||

| N3 | ||

| N4 | ||

| N5 | ||

| N6 | ||

| N7 | ||

| N8 | ||

| N9 | ||

| N10 | ||

| N11 | ||

| N12 | ||

| N13 | ||

| N14 | ||

| P | ||

| Pad # | Name | Description |

| P1 | ||

| P2 | ||

| P3 | ||

| P4 | ||

| P5 | ||

| P6 | ||

| P7 | ||

| P8 | ||

| P9 | ||

| P10 | ||

| P11 | ||

| P12 | ||

| P13 | ||

| P14 | ||

remark: the following Pad #letter's are not used: I, O, Q, S, X, Z, AI, AO, AQ, AS, AX, AZ

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||