Service Connectors: Difference between revisions

Jump to navigation

Jump to search

| (One intermediate revision by the same user not shown) | |||

| Line 296: | Line 296: | ||

|} | |} | ||

== Southbridge == | === Southbridge === | ||

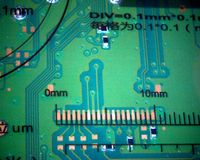

<div style="float:right">[[File:CUH-10xxA - SAA-001 - 20 pins port - img1.jpg|200px|thumb|left|[[CUH-10xxA]] [[SAA-001]] pads2/20 pins - img1]]<br />[[File:CUH-10xxA - SAA-001 - 20 pins port - img2.jpg|200px|thumb|left|[[CUH-10xxA]] [[SAA-001]] pads2/20 pins - img2]]</div> | <div style="float:right">[[File:CUH-10xxA - SAA-001 - 20 pins port - img1.jpg|200px|thumb|left|[[CUH-10xxA]] [[SAA-001]] pads2/20 pins - img1]]<br />[[File:CUH-10xxA - SAA-001 - 20 pins port - img2.jpg|200px|thumb|left|[[CUH-10xxA]] [[SAA-001]] pads2/20 pins - img2]]</div> | ||

| Line 306: | Line 306: | ||

! Pin !! Name !! Description | ! Pin !! Name !! Description | ||

|- | |- | ||

| 1 || || | | 1 || VCC? || | ||

|- | |- | ||

| 2 || Gnd || Internal ground | | 2 || Gnd || Internal ground | ||

| Line 312: | Line 312: | ||

| 3 || || | | 3 || || | ||

|- | |- | ||

| 4 || | | 4 || Gnd || Internal ground | ||

|- | |- | ||

| 5 || || | | 5 || || | ||

| Line 324: | Line 324: | ||

| 9 || || | | 9 || || | ||

|- | |- | ||

| 10 || | | 10 || | ||

|- | |- | ||

| 11 || | | 11 || Gnd || Internal ground | ||

|- | |- | ||

| 12 || || | | 12 || SB-20/S (SDIO?) || probably for eMMC | ||

|- | |- | ||

| 13 || | | 13 || Gnd || Internal ground | ||

|- | |- | ||

| 14 || | | 14 || SB-19/R (SDIO?) || | ||

|- | |- | ||

| 15 || | | 15 || SB SDIO? || | ||

|- | |- | ||

| 16 || | | 16 || SB SDIO? || | ||

|- | |- | ||

| 17 || | | 17 || SB SDIO? || | ||

|- | |- | ||

| 18 || || | | 18 || SB SDIO? || | ||

|- | |- | ||

| 19 || Gnd || Internal ground | | 19 || Gnd || Internal ground | ||

|- | |- | ||

| 20 || | | 20 || NC || | ||

|- | |- | ||

|} | |} | ||

Latest revision as of 00:29, 2 February 2022

JTAG/UART/SPI/Diagnostic I/O used in Sony repair centers if a PS4 could not be fixed by software.

Preproduction Generation[edit | edit source]

Syscon[edit | edit source]

| Pin | Name | Description |

|---|---|---|

| 1 | ||

| 2 | ||

| 3 | ||

| 4 | ||

| 5 | ||

| 6 | ||

| 7 | ||

| 8 | ||

| 9 | ||

| 10 | ||

| 11 | ||

| 12 | ||

| 13 | ||

| 14 | ||

| 15 | ||

| 16 | ||

| 17 | ||

| 18 | ||

| 19 | ||

| 20 | ||

| 21 | ||

| 22 | ||

| 23 | ||

| 24 | ||

| 25 | ||

| 26 | ||

| 27 | ||

| 28 | ||

| 29 | ||

| 30 | ||

| 31 | ||

| 32 |

Southbridge[edit | edit source]

See Aeolia.

| Pin | Name | Description |

|---|---|---|

| 1 | ||

| 2 | ||

| 3 | ||

| 4 | ||

| 5 | ||

| 6 | ||

| 7 | ||

| 8 | ||

| 9 | ||

| 10 | ||

| 11 | ||

| 12 | ||

| 13 | ||

| 14 | ||

| 15 | ||

| 16 | ||

| 17 | ||

| 18 | ||

| 19 | ||

| 20 |

PCIe[edit | edit source]

| Pin | Name | Description |

|---|---|---|

| 1 | ||

| 2 | ||

| 3 | ||

| 4 | ||

| 5 | ||

| 6 | ||

| 7 | ||

| 8 | ||

| 9 | ||

| 10 | ||

| 11 | ||

| 12 | ||

| 13 | ||

| 14 | ||

| 15 | ||

| 16 | ||

| 17 | ||

| 18 | ||

| 19 | ||

| 20 |

| Pin | Name | Description |

|---|---|---|

| 1 | ||

| 2 | ||

| 3 | ||

| 4 | ||

| 5 | ||

| 6 | ||

| 7 | ||

| 8 | ||

| 9 | ||

| 10 | ||

| 11 | ||

| 12 | ||

| 13 | ||

| 14 | ||

| 15 | ||

| 16 | ||

| 17 | ||

| 18 | ||

| 19 | ||

| 20 |

First Generation[edit | edit source]

Syscon[edit | edit source]

See A01-COL.

| Pin | Name | Description |

|---|---|---|

| 1 | VCC? | |

| 2 | NC | No connection |

| 3 | == pin 1 | |

| 4 | ||

| 5 | ||

| 6 | Gnd | Internal ground |

| 7 | I2C | I2C bus (100 kHz clock) -> HDR-D pin 2 |

| 8 | -> HDR-D pin 1 | |

| 9 | Gnd | Internal ground |

| 10 | SC-P70 | |

| 11 | ||

| 12 | SC-P72 | |

| 13 | ||

| 14 | Gnd | Internal ground |

| 15 | SC-P12 | |

| 16 | SC-P11 | |

| 17 | SC-P51 | |

| 18 | Gnd | Internal ground |

| 19 | -> SB? | |

| 20 | -> SB? | |

| 21 | -> SB? | |

| 22 | SC-P40 (TOOL0) open circuit | |

| 23 | Gnd | Internal ground |

| 24 | SC-RESET# | |

| 25 | GND | Internal ground |

| 26 | ||

| 27 | ||

| 28 | SC-P122 | |

| 29 | SC-P121 | |

| 30 | NC | No connection |

Southbridge[edit | edit source]

See Aeolia, Southbridge debug.

| Pin | Name | Description |

|---|---|---|

| 1 | VCC? | |

| 2 | Gnd | Internal ground |

| 3 | ||

| 4 | Gnd | Internal ground |

| 5 | ||

| 6 | ||

| 7 | ||

| 8 | Gnd | Internal ground |

| 9 | ||

| 10 | ||

| 11 | Gnd | Internal ground |

| 12 | SB-20/S (SDIO?) | probably for eMMC |

| 13 | Gnd | Internal ground |

| 14 | SB-19/R (SDIO?) | |

| 15 | SB SDIO? | |

| 16 | SB SDIO? | |

| 17 | SB SDIO? | |

| 18 | SB SDIO? | |

| 19 | Gnd | Internal ground |

| 20 | NC |

Second Generation[edit | edit source]

- TODO