Template:HDMI Controller pinout TQFP 100 pins: Difference between revisions

Jump to navigation

Jump to search

No edit summary |

|||

| (4 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

<br style="clear: both;" /> | <includeonly><br style="clear: both;" /> | ||

<span style="font-size:175%; font-family:Times New Roman;">Pinout</span> | <span style="font-size:175%; font-family:Times New Roman;">Pinout</span> | ||

---- | ---- | ||

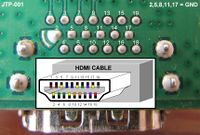

<div style="float:right">[[File:Panasonic-MN8647091.png|200px|thumb|right|Panasonic MN8647091]]<br>[[File:HDMI pads as seen on JTP-001 - (Mr.Dutch).jpg|200px|thumb|right|HDMI connector pads]]<br>[[File:RSX SKEMA.jpg|200px|thumb|right|RSX 41x41 pad layout]]<br>[[File:Mitsumi 348A.jpg|200px|thumb|right|[[Talk:Regulators|Mitsumi 348A]] and<br>[[ISL4353C|Intersil ISL4353C]]<br>Seen on a [[JSD-001]] motherboard]]</div> | </includeonly><div style="float:right">[[File:Panasonic-MN8647091.png|200px|thumb|right|Panasonic MN8647091]]<br>[[File:HDMI pads as seen on JTP-001 - (Mr.Dutch).jpg|200px|thumb|right|HDMI connector pads]]<br>[[File:RSX SKEMA.jpg|200px|thumb|right|RSX 41x41 pad layout]]<br>[[File:Mitsumi 348A.jpg|200px|thumb|right|[[Talk:Regulators|Mitsumi 348A]] and<br>[[ISL4353C|Intersil ISL4353C]]<br>Seen on a [[JSD-001]] motherboard]]</div> | ||

<div style="overflow:auto; <includeonly>height:1400px;</includeonly>"> | <div style="overflow:auto; <includeonly>height:1400px;</includeonly>"> | ||

| Line 13: | Line 13: | ||

| 2 || {{cellcolors|#333|#fff}} GND || {{pin}} || | | 2 || {{cellcolors|#333|#fff}} GND || {{pin}} || | ||

|- | |- | ||

| 3 || {{cellcolors|#ccf}} CEC || {{pinio}} || Connected to [[Connectors#HDMI_Out|HDMI connector]] pin 13 | | 3 || {{cellcolors|#ccf}} CEC || {{pinio}} || Connected to [[Connectors#HDMI_Out|HDMI connector]] pin 13 ([https://en.wikipedia.org/wiki/Consumer_Electronics_Control Consumer Electronics Control]) | ||

|- | |- | ||

| 4 || {{cellcolors|#f83|#fff}} HDMI_VCC2 || {{pin}} || Connected to voltage regulator [[Talk:Regulators|Mitsumi 348A]] pin 5 | | 4 || {{cellcolors|#f83|#fff}} HDMI_VCC2 || {{pin}} || Connected to voltage regulator [[Talk:Regulators|Mitsumi 348A]] pin 5 | ||

| Line 27: | Line 27: | ||

| 9 || {{cellcolors|#f83|#fff}} HDMI_VCC2 || {{pin}} || Connected to voltage regulator [[Talk:Regulators|Mitsumi 348A]] pin 5 | | 9 || {{cellcolors|#f83|#fff}} HDMI_VCC2 || {{pin}} || Connected to voltage regulator [[Talk:Regulators|Mitsumi 348A]] pin 5 | ||

|- | |- | ||

| 10 || {{cellcolors|#ff8}} | | 10 || {{cellcolors|#ff8}} CK- || {{pini}} || Connected to [[Connectors#HDMI_Out|HDMI connector]] pin 12 throught an EMI filter | ||

|- | |- | ||

| 11 || {{cellcolors|#333|#fff}} | | 11 || {{cellcolors|#333|#fff}} CKG || {{pin}} || Connected to [[Connectors#HDMI_Out|HDMI connector]] pin 11 | ||

|- | |- | ||

| 12 || {{cellcolors|#ff8}} | | 12 || {{cellcolors|#ff8}} CK+ || {{pino}} || Connected to [[Connectors#HDMI_Out|HDMI connector]] pin 10 throught an EMI filter | ||

|- | |- | ||

| 13 || {{cellcolors|#f83|#fff}} HDMI_VCC2 || {{pin}} || Connected to voltage regulator [[Talk:Regulators|Mitsumi 348A]] pin 5 | | 13 || {{cellcolors|#f83|#fff}} HDMI_VCC2 || {{pin}} || Connected to voltage regulator [[Talk:Regulators|Mitsumi 348A]] pin 5 | ||

|- | |- | ||

| 14 || {{cellcolors|#ff8}} | | 14 || {{cellcolors|#ff8}} D0- || {{pini}} || Connected to [[Connectors#HDMI_Out|HDMI connector]] pin 9 throught an EMI filter | ||

|- | |- | ||

| 15 || {{cellcolors|#333|#fff}} | | 15 || {{cellcolors|#333|#fff}} D0G || {{pin}} || Connected to [[Connectors#HDMI_Out|HDMI connector]] pin 8 | ||

|- | |- | ||

| 16 || {{cellcolors|#ff8}} | | 16 || {{cellcolors|#ff8}} D0+ || {{pino}} || Connected to [[Connectors#HDMI_Out|HDMI connector]] pin 7 throught an EMI filter | ||

|- | |- | ||

| 17 || {{cellcolors|#f83|#fff}} HDMI_VCC2 || {{pin}} || Connected to voltage regulator [[Talk:Regulators|Mitsumi 348A]] pin 5 | | 17 || {{cellcolors|#f83|#fff}} HDMI_VCC2 || {{pin}} || Connected to voltage regulator [[Talk:Regulators|Mitsumi 348A]] pin 5 | ||

|- | |- | ||

| 18 || {{cellcolors|#ff8}} | | 18 || {{cellcolors|#ff8}} D1- || {{pini}} || Connected to [[Connectors#HDMI_Out|HDMI connector]] pin 6 throught an EMI filter | ||

|- | |- | ||

| 19 || {{cellcolors|#333|#fff}} | | 19 || {{cellcolors|#333|#fff}} D1G || {{pin}} || Connected to [[Connectors#HDMI_Out|HDMI connector]] pin 5 | ||

|- | |- | ||

| 20 || {{cellcolors|#ff8}} | | 20 || {{cellcolors|#ff8}} D1+ || {{pino}} || Connected to [[Connectors#HDMI_Out|HDMI connector]] pin 4 throught an EMI filter | ||

|- | |- | ||

| 21 || {{cellcolors|#f83|#fff}} HDMI_VCC2 || {{pin}} || Connected to voltage regulator [[Talk:Regulators|Mitsumi 348A]] pin 5 | | 21 || {{cellcolors|#f83|#fff}} HDMI_VCC2 || {{pin}} || Connected to voltage regulator [[Talk:Regulators|Mitsumi 348A]] pin 5 | ||

|- | |- | ||

| 22 || {{cellcolors|#ff8}} | | 22 || {{cellcolors|#ff8}} D2- || {{pini}} || Connected to [[Connectors#HDMI_Out|HDMI connector]] pin 3 throught an EMI filter | ||

|- | |- | ||

| 23 || {{cellcolors|#333|#fff}} | | 23 || {{cellcolors|#333|#fff}} D2G || {{pin}} || Connected to [[Connectors#HDMI_Out|HDMI connector]] pin 2 | ||

|- | |- | ||

| 24 || {{cellcolors|#ff8}} | | 24 || {{cellcolors|#ff8}} D2+ || {{pino}} || Connected to [[Connectors#HDMI_Out|HDMI connector]] pin 1 throught an EMI filter | ||

|- | |- | ||

| 25 || {{cellcolors|#f83|#fff}} HDMI_VCC2 || {{pin}} || Connected to voltage regulator [[Talk:Regulators|Mitsumi 348A]] pin 5 | | 25 || {{cellcolors|#f83|#fff}} HDMI_VCC2 || {{pin}} || Connected to voltage regulator [[Talk:Regulators|Mitsumi 348A]] pin 5 | ||

| Line 199: | Line 199: | ||

| 92 || {{cellcolors|#f33|#fff}} HDMI_VCC1 || {{pin}} || Connected to voltage regulator [[Talk:Regulators|Mitsumi 348A]] pin 4 | | 92 || {{cellcolors|#f33|#fff}} HDMI_VCC1 || {{pin}} || Connected to voltage regulator [[Talk:Regulators|Mitsumi 348A]] pin 4 | ||

|- | |- | ||

| 93 || || || Connected to [[Syscon Hardware|Syscon]] pin 124 ([[Template:Syscon_pinout_LQFP_128_pins|LQFP 128 pins layout]]), or pin | | 93 || || || Connected to [[Syscon Hardware|Syscon]] pin 124 ([[Template:Syscon_pinout_LQFP_128_pins|LQFP 128 pins layout]]), or pin 93 ? ([[Template:Syscon_pinout_LQFP_100_pins|LQFP 100 pins layout]]) | ||

|- | |- | ||

| 94 || || || Connected to [[Syscon Hardware|Syscon]] pin 15 ([[Template:Syscon_pinout_LQFP_128_pins|LQFP 128 pins layout]]), or pin | | 94 || || || Connected to [[Syscon Hardware|Syscon]] pin 15 ([[Template:Syscon_pinout_LQFP_128_pins|LQFP 128 pins layout]]), or pin 5 ([[Template:Syscon_pinout_LQFP_100_pins|LQFP 100 pins layout]]) | ||

|- | |- | ||

| 95 || || || Connected to [[Syscon Hardware|Syscon]] pin 120 ([[Template:Syscon_pinout_LQFP_128_pins|LQFP 128 pins layout]]), or pin | | 95 || || || Connected to [[Syscon Hardware|Syscon]] pin 120 ([[Template:Syscon_pinout_LQFP_128_pins|LQFP 128 pins layout]]) through 3.6K resistor, or pin 46 ([[Template:Syscon_pinout_LQFP_100_pins|LQFP 100 pins layout]]) | ||

|- | |- | ||

| 96 || {{cellcolors|#ff8}} | | 96 || {{cellcolors|#ff8}} HPD || {{pini}} || Connected to [[Connectors#HDMI_Out|HDMI connector]] pin 19 (HOTPLUG_DET) | ||

|- | |- | ||

| 97 || {{cellcolors|#66f|#ff0}} | | 97 || {{cellcolors|#66f|#ff0}} DDDATA || {{pinio}} || Connected to [[Connectors#HDMI_Out|HDMI connector]] pin 16 ([https://en.wikipedia.org/wiki/Display_Data_Channel Display Data Channel], data) | ||

|- | |- | ||

| 98 || {{cellcolors|#66f|#ff0}} | | 98 || {{cellcolors|#66f|#ff0}} DDCLK || {{pino}} || Connected to [[Connectors#HDMI_Out|HDMI connector]] pin 15 ([https://en.wikipedia.org/wiki/Display_Data_Channel Display Data Channel], clock) | ||

|- | |- | ||

| 99 || {{cellcolors|#f83|#fff}} HDMI_VCC2 || {{pin}} || Connected to voltage regulator [[Talk:Regulators|Mitsumi 348A]] pin 5 | | 99 || {{cellcolors|#f83|#fff}} HDMI_VCC2 || {{pin}} || Connected to voltage regulator [[Talk:Regulators|Mitsumi 348A]] pin 5 | ||

Latest revision as of 06:31, 20 July 2022

| Pin | Name | Type | Description |

|---|---|---|---|

| 1 | N/C ? | Not connected ? | |

| 2 | GND | ||

| 3 | CEC | Connected to HDMI connector pin 13 (Consumer Electronics Control) | |

| 4 | HDMI_VCC2 | Connected to voltage regulator Mitsumi 348A pin 5 | |

| 5 | GND | ||

| 6 | N/C ? | Not connected ? | |

| 7 | GND | ||

| 8 | N/C ? | Not connected ? | |

| 9 | HDMI_VCC2 | Connected to voltage regulator Mitsumi 348A pin 5 | |

| 10 | CK- | Connected to HDMI connector pin 12 throught an EMI filter | |

| 11 | CKG | Connected to HDMI connector pin 11 | |

| 12 | CK+ | Connected to HDMI connector pin 10 throught an EMI filter | |

| 13 | HDMI_VCC2 | Connected to voltage regulator Mitsumi 348A pin 5 | |

| 14 | D0- | Connected to HDMI connector pin 9 throught an EMI filter | |

| 15 | D0G | Connected to HDMI connector pin 8 | |

| 16 | D0+ | Connected to HDMI connector pin 7 throught an EMI filter | |

| 17 | HDMI_VCC2 | Connected to voltage regulator Mitsumi 348A pin 5 | |

| 18 | D1- | Connected to HDMI connector pin 6 throught an EMI filter | |

| 19 | D1G | Connected to HDMI connector pin 5 | |

| 20 | D1+ | Connected to HDMI connector pin 4 throught an EMI filter | |

| 21 | HDMI_VCC2 | Connected to voltage regulator Mitsumi 348A pin 5 | |

| 22 | D2- | Connected to HDMI connector pin 3 throught an EMI filter | |

| 23 | D2G | Connected to HDMI connector pin 2 | |

| 24 | D2+ | Connected to HDMI connector pin 1 throught an EMI filter | |

| 25 | HDMI_VCC2 | Connected to voltage regulator Mitsumi 348A pin 5 | |

| 26 | HDMI_VCC2 | Connected to voltage regulator Mitsumi 348A pin 5 | |

| 27 | HDMI_I2C_SCL | Connected to Syscon pin 1 (LQFP 128 pins layout), or pin 1 (LQFP 100 pins layout) | |

| 28 | GND | ||

| 29 | HDMI_I2C_SDA | Connected to Syscon pin 128 (LQFP 128 pins layout), or pin 100 (LQFP 100 pins layout) | |

| 30 | HDMI_VCC1 | Connected to voltage regulator Mitsumi 348A pin 4 | |

| 31 | Connected to RSX pad ? (RSX layout 41x41), or pad ? (RSX layout 34x34) | ||

| 32 | |||

| 33 | |||

| 34 | GND | ||

| 35 | |||

| 36 | |||

| 37 | |||

| 38 | HDMI_VCC2 | Connected to voltage regulator Mitsumi 348A pin 5 | |

| 39 | |||

| 40 | |||

| 41 | |||

| 42 | HDMI_VCC1 | Connected to voltage regulator Mitsumi 348A pin 4 | |

| 43 | |||

| 44 | |||

| 45 | |||

| 46 | GND | ||

| 47 | |||

| 48 | |||

| 49 | |||

| 50 | HDMI_VCC1 | Connected to voltage regulator Mitsumi 348A pin 4 | |

| 51 | |||

| 52 | |||

| 53 | |||

| 54 | |||

| 55 | |||

| 56 | |||

| 57 | HDMI_VCC2 | Connected to voltage regulator Mitsumi 348A pin 5 | |

| 58 | |||

| 59 | |||

| 60 | |||

| 61 | GND | ||

| 62 | |||

| 63 | |||

| 64 | |||

| 65 | HDMI_VCC1 | Connected to voltage regulator Mitsumi 348A pin 4 | |

| 66 | |||

| 67 | |||

| 68 | |||

| 69 | GND | ||

| 70 | |||

| 71 | |||

| 72 | |||

| 73 | HDMI_VCC1 | Connected to voltage regulator Mitsumi 348A pin 4 | |

| 74 | |||

| 75 | |||

| 76 | |||

| 77 | HDMI_VCC2 | Connected to voltage regulator Mitsumi 348A pin 5 | |

| 78 | |||

| 79 | |||

| 80 | |||

| 81 | |||

| 82 | HDMI_VCC1 | Connected to voltage regulator Mitsumi 348A pin 4 | |

| 83 | |||

| 84 | |||

| 85 | |||

| 86 | Connected to Intersil ISL4353C optical audio pin 24 | ||

| 87 | HDMI_VCC2 | Connected to voltage regulator Mitsumi 348A pin 5 | |

| 88 | Connected to Intersil ISL4353C optical audio pin 1 | ||

| 89 | Connected to Intersil ISL4353C optical audio pin 23 | ||

| 90 | GND | ||

| 91 | |||

| 92 | HDMI_VCC1 | Connected to voltage regulator Mitsumi 348A pin 4 | |

| 93 | Connected to Syscon pin 124 (LQFP 128 pins layout), or pin 93 ? (LQFP 100 pins layout) | ||

| 94 | Connected to Syscon pin 15 (LQFP 128 pins layout), or pin 5 (LQFP 100 pins layout) | ||

| 95 | Connected to Syscon pin 120 (LQFP 128 pins layout) through 3.6K resistor, or pin 46 (LQFP 100 pins layout) | ||

| 96 | HPD | Connected to HDMI connector pin 19 (HOTPLUG_DET) | |

| 97 | DDDATA | Connected to HDMI connector pin 16 (Display Data Channel, data) | |

| 98 | DDCLK | Connected to HDMI connector pin 15 (Display Data Channel, clock) | |

| 99 | HDMI_VCC2 | Connected to voltage regulator Mitsumi 348A pin 5 | |

| 100 | HDMI_VCC1 | Connected to voltage regulator Mitsumi 348A pin 4 | |