CXD90062GG: Difference between revisions

Jump to navigation

Jump to search

(Add DDR4 pinout) |

|||

| Line 7: | Line 7: | ||

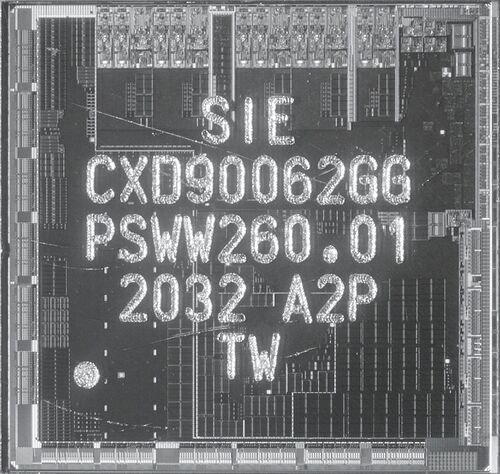

[[File:50980106477 3117f2d5c0 o.jpg|500px]] | [[File:50980106477 3117f2d5c0 o.jpg|500px]] | ||

[[File:CXD90062GG_Proto.png]] | [[File:CXD90062GG_Proto.png]] | ||

== Pinout == | |||

DDR4 | |||

{| class="wikitable mw-collapsible" | |||

|+ | |||

!Pad | |||

!Internal Name | |||

!External Name | |||

!Type | |||

!Description | |||

|- | |||

|AA12 | |||

|PIN_VREFSMIO | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|AB7 | |||

|PIN_M_A[15] | |||

|S50_FC_DDR_A15 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AB8 | |||

|PIN_M_A[11] | |||

|S50_FC_DDR_A11 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AB9 | |||

|PIN_M_A[8] | |||

|S50_FC_DDR_A8 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AB10 | |||

|PIN_M_A[4] | |||

|S50_FC_DDR_A4 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AB11 | |||

|PIN_M_ALERT_N | |||

|S50_/FC_DDR_ALERTN | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AB12 | |||

|PIN_DDR_CAL | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|AB13 | |||

|PIN_M_ODT[0] | |||

|S50_FC_DDR_ODT0 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AB14 | |||

|PIN_M_CS_N[0] | |||

|S50_FC_DDR_CS0N | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AB15 | |||

|PIN_M_D[7] | |||

|S50_FC_DDR_D7 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|AB16 | |||

|PIN_M_D[6] | |||

|S50_FC_DDR_D6 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|AB17 | |||

|PIN_M_D[2] | |||

|S50_FC_DDR_D2 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|AB18 | |||

|PIN_M_D[1] | |||

|S50_FC_DDR_D1 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|AB19 | |||

|PIN_M_DM | |||

|S50_FC_DDR_DM | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AC7 | |||

|PIN_M_A[14] | |||

|S50_FC_DDR_A14 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AC9 | |||

|PIN_M_A[7] | |||

|S50_FC_DDR_A7 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AC10 | |||

|PIN_M_A[3] | |||

|S50_FC_DDR_A3 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AC12 | |||

|PIN_M_PAR | |||

|S50_FC_DDR_PAR | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AC14 | |||

|PIN_M_CS_N[1] | |||

|N/C | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

|No Connection | |||

|- | |||

|AC15 | |||

|PIN_M_WE_N | |||

|S50_FC_DDR_WEN | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AC17 | |||

|PIN_M_D[3] | |||

|S50_FC_DDR_D3 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|AC19 | |||

|PIN_M_D[0] | |||

|S50_FC_DDR_D0 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|AD7 | |||

|PIN_M_A[13] | |||

|S50_FC_DDR_A13 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AD8 | |||

|PIN_M_A[9] | |||

|S50_FC_DDR_A9 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AD9 | |||

|PIN_M_A[6] | |||

|S50_FC_DDR_A6 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AD10 | |||

|PIN_M_A[2] | |||

|S50_FC_DDR_A2 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AD11 | |||

|PIN_M_BA[2] | |||

|S50_FC_DDR_BA2 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AD12 | |||

|PIN_M_BA[0] | |||

|S50_FC_DDR_BA0 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AD13 | |||

|PIN_M_ODT[1] | |||

|N/C | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

|No Connection | |||

|- | |||

|AD14 | |||

|PIN_M_CKE[0] | |||

|S50_FC_DDR_CKE0 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AD15 | |||

|PIN_M_CAS_N | |||

|S50_/FC_DDR_CASN | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AD16 | |||

|PIN_M_CLOCK[0] | |||

|D90_FC_DDR_CLOCK0_P | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AD17 | |||

|PIN_M_D[4] | |||

|S50_FC_DDR_D4 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|AD18 | |||

|PIN_M_DQS_P[0] | |||

|D90_FC_DDR_DQS0_P | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|AE7 | |||

|PIN_M_A[12] | |||

|S50_FC_DDR_A12 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AE8 | |||

|PIN_M_A[10] | |||

|S50_FC_DDR_A10 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AE9 | |||

|PIN_M_A[5] | |||

|S50_FC_DDR_A5 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AE10 | |||

|PIN_M_A[1] | |||

|S50_FC_DDR_A1 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AE11 | |||

|PIN_M_A[0] | |||

|S50_FC_DDR_A0 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AE12 | |||

|PIN_M_BA[1] | |||

|S50_FC_DDR_BA1 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AE13 | |||

|PIN_M_RST_N | |||

|NS50_/FC_DDR_RSTN | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AE14 | |||

|PIN_M_CKE[1] | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|AE15 | |||

|PIN_M_RAS_N | |||

|S50_/FC_DDR_RASN | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AE16 | |||

|PIN_M_CLOCK_N[0] | |||

|D90_FC_DDR_CLOCK0_N | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AE17 | |||

|PIN_M_D[5] | |||

|S50_FC_DDR_D5 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|AE18 | |||

|PIN_M_DQS_N[0] | |||

|D90_FC_DDR_DQS0_N | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|} | |||

== Sources == | == Sources == | ||

https://www.flickr.com/photos/130561288@N04/albums/72157718290760702 | https://www.flickr.com/photos/130561288@N04/albums/72157718290760702 | ||

Revision as of 23:09, 11 December 2024

NVME Controller

Pictures

Pinout

DDR4

Sources

https://www.flickr.com/photos/130561288@N04/albums/72157718290760702