CXD90062GG: Difference between revisions

Jump to navigation

Jump to search

(→Pinout: change pins order) |

No edit summary |

||

| Line 1: | Line 1: | ||

* NVME Controller, Codename Titania | * NVME Controller, Codename ZAO/Titania | ||

Revision as of 03:10, 12 March 2025

- NVME Controller, Codename ZAO/Titania

Pinout

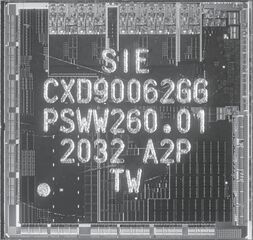

Pictures

Sources

https://www.flickr.com/photos/130561288@N04/albums/72157718290760702