CXD90062GG: Difference between revisions

Jump to navigation

Jump to search

(→Pinout: Added all channels) |

(→Pinout: Added all pins) |

||

| Line 11: | Line 11: | ||

!Type | !Type | ||

!Description | !Description | ||

|- | |||

|A1 | |||

|VSS_A1 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|A2 | |||

|VSS_A2 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|A3 | |A3 | ||

| Line 22: | Line 34: | ||

|S50_NAND_CH6_CLE | |S50_NAND_CH6_CLE | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | |||

|- | |||

|A5 | |||

|PIN_AD_CH7[1] | |||

|S50_NAND_CH7_AD1 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | | | ||

|- | |- | ||

| Line 27: | Line 45: | ||

|PIN_DQSB_CH7 | |PIN_DQSB_CH7 | ||

|D90_NAND_CH7_DQS_N | |D90_NAND_CH7_DQS_N | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|A7 | |||

|PIN_AD_CH7[7] | |||

|S50_NAND_CH7_AD7 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

| Line 126: | Line 150: | ||

| | | | ||

|- | |- | ||

| | |A24 | ||

| | |VSS_A24 | ||

| | |GND | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |A25 | ||

| | |VSS_A25 | ||

| | |GND | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

|AA1 | |AA1 | ||

|PIN_AD_CH1[1] | |PIN_AD_CH1[1] | ||

|S50_NAND_CH1_AD1 | |S50_NAND_CH1_AD1 | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

| Line 149: | Line 173: | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |||

|AA3 | |||

|VSS_AA3 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|AA4 | |AA4 | ||

| Line 168: | Line 198: | ||

| | | | ||

|- | |- | ||

| | |AA7 | ||

| | |VSS_AA7 | ||

| | |GND | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |AA8 | ||

| | |VSS_AA8 | ||

| | |GND | ||

|[[File:Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

|AA15 | |AA9 | ||

|PIN_SOC_V_RST | |VSS_AA9 | ||

|/FC_RESET | |GND | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|AA10 | |||

|VSS_AA10 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|AA11 | |||

|VSS_AA11 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|AA12 | |||

|PIN_VREFSMIO | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|AA13 | |||

|VSS_AA13 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|AA14 | |||

|PIN_GPIO_7 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|AA15 | |||

|PIN_SOC_V_RST | |||

|/FC_RESET | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

| Line 216: | Line 282: | ||

| | | | ||

|- | |- | ||

|AA24 | |AA21 | ||

|PIN_REFCLK_P_0 | |VSS_AA21 | ||

|D100G_FC_PCIE_CLK_P | |GND | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|AA22 | |||

|VSS_AA22 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|AA23 | |||

|VSS_AA23 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|AA24 | |||

|PIN_REFCLK_P_0 | |||

|D100G_FC_PCIE_CLK_P | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

| Line 257: | Line 341: | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |||

|AB6 | |||

|VSS_AB6 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|AB7 | |AB7 | ||

| Line 353: | Line 443: | ||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |[[File:Pin-nc.png|alt=Not connected|frameless]] | ||

| | | | ||

|- | |||

|AB23 | |||

|VSS_AB23 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|AB24 | |||

|VSS_AB24 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|AB25 | |||

|VSS_AB25 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|AC1 | |AC1 | ||

| Line 365: | Line 473: | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |||

|AC3 | |||

|VSS_AC3 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|AC4 | |AC4 | ||

| Line 377: | Line 491: | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |||

|AC6 | |||

|VSS_AC6 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|AC7 | |AC7 | ||

| Line 383: | Line 503: | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |||

|AC8 | |||

|VSS_AC8 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|AC9 | |AC9 | ||

| Line 395: | Line 521: | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |||

|AC11 | |||

|VSS_AC11 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|AC12 | |AC12 | ||

| Line 401: | Line 533: | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |||

|AC13 | |||

|VSS_AC13 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|AC14 | |AC14 | ||

| Line 413: | Line 551: | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |||

|AC16 | |||

|VSS_AC16 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|AC17 | |AC17 | ||

| Line 419: | Line 563: | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |||

|AC18 | |||

|VSS_AC18 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|AC19 | |AC19 | ||

| Line 443: | Line 593: | ||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |[[File:Pin-nc.png|alt=Not connected|frameless]] | ||

| | | | ||

|- | |||

|AC23 | |||

|VSS_AC23 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|AC24 | |AC24 | ||

| Line 455: | Line 611: | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |||

|AD1 | |||

|VSS_AD1 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|AD2 | |AD2 | ||

| Line 480: | Line 642: | ||

| | | | ||

|- | |- | ||

|AD7 | |AD6 | ||

|VSS_AD6 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|AD7 | |||

|PIN_M_A[13] | |PIN_M_A[13] | ||

|S50_FC_DDR_A13 | |S50_FC_DDR_A13 | ||

| Line 551: | Line 719: | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |||

|AD19 | |||

|VSS_AD19 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|AD20 | |AD20 | ||

| Line 581: | Line 755: | ||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |[[File:Pin-nc.png|alt=Not connected|frameless]] | ||

| | | | ||

|- | |||

|AD25 | |||

|VSS_AD25 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|AE1 | |||

|VSS_AE1 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|AE2 | |||

|VSS_AE2 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|AE3 | |AE3 | ||

| Line 599: | Line 791: | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |||

|AE6 | |||

|VSS_AE6 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|AE7 | |AE7 | ||

| Line 671: | Line 869: | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |||

|AE19 | |||

|VSS_AE19 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|AE20 | |AE20 | ||

| Line 696: | Line 900: | ||

| | | | ||

|- | |- | ||

|B2 | |AE24 | ||

|PIN_AD_CH6[6] | |VSS_AE24 | ||

|S50_NAND_CH6_AD6 | |GND | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|AE25 | |||

|VSS_AE25 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|B1 | |||

|VSS_B1 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|B2 | |||

|PIN_AD_CH6[6] | |||

|S50_NAND_CH6_AD6 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

| Line 821: | Line 1,043: | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |||

|B23 | |||

|VSS_B23 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|B24 | |||

|VSS_B24 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|B25 | |||

|VSS_B25 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|C1 | |C1 | ||

| Line 833: | Line 1,073: | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |||

|C3 | |||

|VSS_C3 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|C4 | |C4 | ||

| Line 845: | Line 1,091: | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |||

|C6 | |||

|VSS_C6 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|C7 | |C7 | ||

| Line 852: | Line 1,104: | ||

| | | | ||

|- | |- | ||

|C9 | |C8 | ||

|VSS_C8 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|C9 | |||

|PIN_CE1_CH7 | |PIN_CE1_CH7 | ||

|S50_/NAND_CH7_CE1 | |S50_/NAND_CH7_CE1 | ||

| Line 863: | Line 1,121: | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |||

|C11 | |||

|VSS_C11 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|C12 | |C12 | ||

| Line 875: | Line 1,139: | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |||

|C14 | |||

|VSS_C14 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|C15 | |C15 | ||

| Line 887: | Line 1,157: | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |||

|C17 | |||

|VSS_C17 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|C18 | |C18 | ||

| Line 905: | Line 1,181: | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |||

|C21 | |||

|VSS_C21 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|C22 | |||

|VSS_C22 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|C23 | |||

|VSS_C23 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|C24 | |C24 | ||

| Line 1,031: | Line 1,325: | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |||

|D20 | |||

|VSS_D20 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|D21 | |D21 | ||

| Line 1,044: | Line 1,344: | ||

| | | | ||

|- | |- | ||

|E1 | |D23 | ||

|VSS_D23 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|D24 | |||

|VSS_D24 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|D25 | |||

|VSS_D25 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|E1 | |||

|PIN_RE_CH5 | |PIN_RE_CH5 | ||

|D90_NAND_CH5_RE_ P | |D90_NAND_CH5_RE_ P | ||

| Line 1,055: | Line 1,373: | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |||

|E3 | |||

|VSS_E3 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|E4 | |E4 | ||

| Line 1,157: | Line 1,481: | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |||

|E21 | |||

|VSS_E21 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|E22 | |||

|VSS_E22 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|E23 | |||

|VSS_E23 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|E24 | |E24 | ||

| Line 1,223: | Line 1,565: | ||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |[[File:Pin-nc.png|alt=Not connected|frameless]] | ||

| | | | ||

|- | |||

|F10 | |||

|VSS_F10 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|F11 | |F11 | ||

| Line 1,278: | Line 1,626: | ||

| | | | ||

|- | |- | ||

|F21 | |F20 | ||

|VSS_F20 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|F21 | |||

|PIN_TXN_RC1_1 | |PIN_TXN_RC1_1 | ||

|D85_M2_PCIE_TX1N | |D85_M2_PCIE_TX1N | ||

| Line 1,289: | Line 1,643: | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |||

|F23 | |||

|VSS_F23 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|F24 | |||

|VSS_F24 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|F25 | |||

|VSS_F25 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|G1 | |G1 | ||

| Line 1,325: | Line 1,697: | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |||

|G7 | |||

|VSS_G7 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|G8 | |||

|VSS_G8 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|G9 | |||

|VSS_G9 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|G10 | |||

|VSS_G10 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|G11 | |G11 | ||

| Line 1,332: | Line 1,728: | ||

| | | | ||

|- | |- | ||

|G14 | |G12 | ||

|VSS_G12 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|G13 | |||

|VSS_G13 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|G14 | |||

|PIN_CE3_CH9 | |PIN_CE3_CH9 | ||

| | | | ||

| Line 1,343: | Line 1,751: | ||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |[[File:Pin-nc.png|alt=Not connected|frameless]] | ||

| | | | ||

|- | |||

|G16 | |||

|VSS_G16 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|G17 | |G17 | ||

| Line 1,367: | Line 1,781: | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |||

|G21 | |||

|VSS_G21 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|G22 | |||

|VSS_G22 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|G23 | |||

|VSS_G23 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|G24 | |G24 | ||

| Line 1,391: | Line 1,823: | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |||

|H3 | |||

|VSS_H3 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

|H4 | |H4 | ||

| Line 1,416: | Line 1,854: | ||

| | | | ||

|- | |- | ||

| | |H8 | ||

| | |VSS_H8 | ||

| | |GND | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |H9 | ||

| | |VSS_H9 | ||

| | |GND | ||

|[[File:Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |||

|H10 | |||

|VSS_H10 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|H11 | |||

|VSS_H11 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

| | |H12 | ||

| | |VSS_H12 | ||

| | |GND | ||

|[[File:Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |H13 | ||

| | |PIN_VREF_NF[1] | ||

| | |1.2V_FC_VDDQFIO | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |H14 | ||

| | |VSS_H14 | ||

| | |GND | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

|Ground | |||

|- | |||

|H15 | |||

|VSS_H15 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|H16 | |||

|VSS_H16 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|H17 | |||

|VSS_H17 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|H18 | |||

|PIN_CE3_CH11 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | | | ||

|- | |- | ||

| | |H19 | ||

| | |PIN_CE2_CH11 | ||

| | | | ||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

|[[File:Pin | |||

| | | | ||

|- | |- | ||

| | |H20 | ||

| | |VSS_H20 | ||

| | |GND | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|H21 | |||

|PIN_TXN_RC1_2 | |||

|D85_M2_PCIE_TX2N | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |- | ||

| | |H22 | ||

| | |PIN_TXP_RC1_2 | ||

| | |D85_M2_PCIE_TX2P | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |- | ||

|J5 | |H23 | ||

|PIN_CE0_CH4 | |VSS_H23 | ||

|S50_/NAND_CH4_CE0 | |GND | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|H24 | |||

|VSS_H24 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|H25 | |||

|VSS_H25 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|J1 | |||

|PIN_REB_CH4 | |||

|D90_NAND_CH4_RE_ N S50_/ | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|J2 | |||

|PIN_RE_CH4 | |||

|D90_NAND_CH4_RE_ P | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|J3 | |||

|PIN_CLE_CH4 | |||

|S50_NAND_CH4_CLE | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|J4 | |||

|PIN_ALE_CH4 | |||

|S50_NAND_CH4_ALE | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|J5 | |||

|PIN_CE0_CH4 | |||

|S50_/NAND_CH4_CE0 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

| Line 1,488: | Line 2,004: | ||

| | | | ||

|- | |- | ||

| | |J8 | ||

| | |VSS_J8 | ||

| | |GND | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |J9 | ||

| | |VSS_J9 | ||

| | |GND | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|J10 | |||

|VDDOFIO_J10 | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |J11 | ||

| | |VDDOFIO_J11 | ||

| | |1.2V_FC_VDDQFIO | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |J12 | ||

| | |VDDOFIO_J12 | ||

| | |1.2V_FC_VDDQFIO | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |J13 | ||

| | |VSS_J13 | ||

| | |GND | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

|Ground | |||

|- | |||

|J14 | |||

|VDDOFIO_J14 | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | | | ||

|- | |- | ||

| | |J15 | ||

| | |VDDOFIO_J15 | ||

| | |1.2V_FC_VDDQFIO | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |J16 | ||

| | |VDDOFIO_J16 | ||

| | |1.2V_FC_VDDQFIO | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |J17 | ||

| | |VSS_J17 | ||

| | |GND | ||

|[[File:Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |J18 | ||

| | |VSS_J18 | ||

| | |GND | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |J19 | ||

| | |VSS_J19 | ||

| | |GND | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |J20 | ||

| | |VSS_J20 | ||

| | |GND | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

|Ground | |||

|- | |||

|J21 | |||

|VSS_J21 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|J22 | |||

|VSS_J22 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|J23 | |||

|VSS_J23 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|J24 | |||

|PIN_RXN_RC1_3 | |||

|D85_M2_PCIE_RX3N | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | | | ||

|- | |- | ||

| | |J25 | ||

| | |PIN_RXP_RC1_3 | ||

| | |D85_M2_PCIE_RX3P | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |K1 | ||

|PIN_AD_CH4[ | |PIN_AD_CH4[4] | ||

| | |S50_NAND_CH4_AD4 | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |- | ||

| | |K2 | ||

|PIN_AD_CH4[ | |PIN_AD_CH4[5] | ||

| | |S50_NAND_CH4_AD5 | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |- | ||

| | |K3 | ||

|PIN_AD_CH4[ | |VSS_K3 | ||

| | |GND | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|K4 | |||

|PIN_AD_CH4[6] | |||

|S50_NAND_CH4_AD6 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |- | ||

| | |K5 | ||

|PIN_AD_CH4[ | |PIN_AD_CH4[7] | ||

| | |S50_NAND_CH4_AD7 | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |- | ||

| | |K6 | ||

| | |PIN_WE_CH4 | ||

| | |NAND_CH4_WE | ||

|[[File: | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |- | ||

| | |K7 | ||

| | |PIN_CE2_CH4 | ||

| | | | ||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

|[[File:Pin | |||

| | | | ||

|- | |- | ||

| | |K8 | ||

| | |VSS_K8 | ||

| | |GND | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |K9 | ||

| | |VSS_K9 | ||

| | |GND | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |K10 | ||

| | |VDD_K10 | ||

| | |0.8V_FC_VDD | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |K11 | ||

| | |VDD_K11 | ||

| | |0.8V_FC_VDD | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |K12 | ||

| | |VSS_K12 | ||

| | |GND | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |K13 | ||

| | |VSS_K13 | ||

| | |GND | ||

|[[File:Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |K14 | ||

| | |VDD_K14 | ||

| | |0.8V_FC_VDD | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |K15 | ||

| | |VDD_K15 | ||

| | |0.8V_FC_VDD | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |K16 | ||

| | |VSS_K16 | ||

| | |GND | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |K17 | ||

| | |VSS_K17 | ||

| | |GND | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |||

|K18 | |||

|VSS_K18 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|K19 | |||

|VSS_K19 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|K20 | |||

|VSS_K20 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

| | |K21 | ||

| | |PIN_TXN_RC1_3 | ||

| | |D85_M2_PCIE_TX3N | ||

|[[File: | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |- | ||

| | |K22 | ||

| | |PIN_TXP_RC1_3 | ||

| | |D85_M2_PCIE_TX3P | ||

|[[File: | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |- | ||

| | |K23 | ||

| | |VSS_K23 | ||

| | |GND | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|K24 | |||

|VSS_K24 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|K25 | |||

|VSS_K25 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|L1 | |||

|PIN_DQS_CH4 | |||

|D90_NAND_CH4_DQS_P | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |- | ||

| | |L2 | ||

| | |PIN_DQSB_CH4 | ||

| | |D90_NAND_CH4_DQS_N | ||

|[[File:Pin | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |- | ||

| | |L3 | ||

| | |PIN_AD_CH4[3] | ||

| | |S50_NAND_CH4_AD3 | ||

|[[File:Pin- | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |- | ||

| | |L4 | ||

| | |PIN_AD_CH4[2] | ||

| | |S50_NAND_CH4_AD2 | ||

|[[File:IC-Pin- | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |- | ||

| | |L5 | ||

|PIN_AD_CH4[1] | |||

|S50_NAND_CH4_AD1 | |||

|[ | |||

| | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |- | ||

| | |L6 | ||

| | |PIN_AD_CH4[0] | ||

| | |S50_NAND_CH4_AD0 | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |- | ||

| | |L7 | ||

| | |VSS_L7 | ||

| | |GND | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

|Ground | |||

|- | |||

|L8 | |||

|VSS_L8 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|L9 | |||

|VDDOFIO_L9 | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | | | ||

|- | |- | ||

| | |L10 | ||

| | |VSS_L10 | ||

| | |GND | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |||

|L11 | |||

|VSS_L11 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

| | |L12 | ||

| | |VDD_L12 | ||

| | |0.8V_FC_VDD | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |L13 | ||

| | |VDD_L13 | ||

| | |0.8V_FC_VDD | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |L14 | ||

| | |VSS_L14 | ||

| | |GND | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |L15 | ||

| | |VSS_L15 | ||

| | |GND | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |L16 | ||

| | |VDD_L16 | ||

| | |0.8V_FC_VDD | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |L17 | ||

| | |AVDD18_PCIE_L17 | ||

| | |1.8V_FC_AVDD | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |L18 | ||

| | |VSS_L18 | ||

| | |GND | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |L19 | ||

| | |VSS_L19 | ||

| | |GND | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |L20 | ||

| | |VSS_L20 | ||

| | |GND | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |L21 | ||

| | |VSS_L21 | ||

| | |GND | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |L22 | ||

| | |VSS_L22 | ||

| | |GND | ||

|[[File:Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |L23 | ||

| | |VSS_L23 | ||

| | |GND | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |L24 | ||

| | |PIN_RXN_EP_0 | ||

| | |D85_SOC_PCIE_TX3P | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |L25 | ||

| | |PIN_RXP_EP_0 | ||

| | |D85_SOC_PCIE_TX3N | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |M1 | ||

| | |PIN_REB_CH3 | ||

| | |D90_NAND_CH3_RE_ N S50_/ | ||

|[[File: | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |- | ||

| | |M2 | ||

| | |PIN_RE_CH3 | ||

| | |D90_NAND_CH3_RE_ P | ||

|[[File: | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |- | ||

| | |M3 | ||

| | |PIN_CE1_CH3 | ||

| | |S50_/NAND_CH3_CE1 | ||

|[[File: | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |- | ||

| | |M4 | ||

| | |PIN_CE0_CH3 | ||

| | |S50_/NAND_CH3_CE0 | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |- | ||

| | |M5 | ||

| | |PIN_ALE_CH3 | ||

| | |S50_NAND_CH3_ALE | ||

|[[File:Pin | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |- | ||

| | |M6 | ||

| | |PIN_CLE_CH3 | ||

| | |S50_NAND_CH3_CLE | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |- | ||

| | |M7 | ||

| | |PIN_CE2_CH3 | ||

| | | | ||

|[[File:Pin | |[[File:Pin-nc.png|alt=Not connected|frameless]] | ||

| | | | ||

|- | |- | ||

| | |M8 | ||

| | |PIN_CAL_NF | ||

| | |S50_/NAND_WP | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |- | ||

| | |M9 | ||

| | |VDDOFIO_M9 | ||

| | |1.2V_FC_VDDQFIO | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |M10 | ||

| | |VDD_M10 | ||

| | |0.8V_FC_VDD | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |M11 | ||

| | |VDD_M11 | ||

| | |0.8V_FC_VDD | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |M12 | ||

| | |VSS_M12 | ||

| | |GND | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |M13 | ||

| | |VSS_M13 | ||

| | |GND | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |M14 | ||

| | |VDD_M14 | ||

| | |0.8V_FC_VDD | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |M15 | ||

| | |VDD_M15 | ||

| | |0.8V_FC_VDD | ||

|[[File:Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |M16 | ||

| | |VSS_M16 | ||

| | |GND | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |M17 | ||

| | |AVDD18_PCIE_M17 | ||

| | |1.8V_FC_AVDD | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |M18 | ||

| | |VSS_M18 | ||

| | |GND | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |M19 | ||

| | |VSS_M19 | ||

| | |GND | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |M20 | ||

| | |VSS_M20 | ||

| | |GND | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |M21 | ||

| | |PIN_TXN_EP_0 | ||

| | |D85_SOC_PCIE_RX3P | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |- | ||

| | |M22 | ||

| | |PIN_TXP_EP_0 | ||

| | |D85_SOC_PCIE_RX3N | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | | | ||

|- | |- | ||

| | |M23 | ||

| | |VSS_M23 | ||

| | |GND | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |||

|M24 | |||

|VSS_M24 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |- | ||

| | |M25 | ||

| | |VSS_M25 | ||

| | |GND | ||

|[[File:Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |N1 | ||

| | |PIN_AD_CH3[7] | ||

| | |S50_NAND_CH3_AD7 | ||

|[[File:Pin- | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |- | ||

| | |N2 | ||

| | |PIN_AD_CH3[6] | ||

|S50_NAND_CH3_AD6 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | | | ||

|[[File:Pin- | |- | ||

|N3 | |||

|VSS_N3 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|N4 | |||

|PIN_AD_CH3[5] | |||

|S50_NAND_CH3_AD5 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | | | ||

|- | |- | ||

| | |N5 | ||

| | |PIN_AD_CH3[4] | ||

|S50_NAND_CH3_AD4 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | | | ||

|[[File:Pin | |- | ||

|N6 | |||

|PIN_WE_CH3 | |||

|NAND_CH3_WE | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | | | ||

|- | |- | ||

| | |N7 | ||

| | |PIN_CE3_CH3 | ||

| | | | ||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |[[File:Pin-nc.png|alt=Not connected|frameless]] | ||

| | | | ||

|- | |- | ||

| | |N8 | ||

| | |PIN_VREF_NF[0] | ||

| | |1.2V_FC_VDDQFIO | ||

|[[File:Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |N9 | ||

| | |VSS_N9 | ||

| | |GND | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |N10 | ||

| | |VSS_N10 | ||

| | |GND | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |N11 | ||

| | |VSS_N11 | ||

| | |GND | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |N12 | ||

| | |VDD_N12 | ||

| | |0.8V_FC_VDD | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |N13 | ||

| | |VDD_N13 | ||

| | |0.8V_FC_VDD | ||

|[[File:IC-Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |N14 | ||

| | |VSS_N14 | ||

| | |GND | ||

|[[File:Pin | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |N15 | ||

| | |VSS_N15 | ||

| | |GND | ||

|[[File:Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |N16 | ||

| | |VDD_N16 | ||

| | |0.8V_FC_VDD | ||

|[[File:Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |N17 | ||

| | |VSS_N17 | ||

| | |GND | ||

|[[File:Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |N18 | ||

| | |VSS_N18 | ||

| | |GND | ||

|[[File:Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |N19 | ||

| | |VSS_N19 | ||

| | |GND | ||

|[[File:Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |N20 | ||

| | |VSS_N20 | ||

| | |GND | ||

|[[File:Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |N21 | ||

| | |VSS_N21 | ||

| | |GND | ||

|[[File:Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |N22 | ||

| | |VSS_N22 | ||

|GND | |GND | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

|Ground | |Ground | ||

|- | |- | ||

| | |N23 | ||

| | |VSS_N23 | ||

| | |GND | ||

|[[File:Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |N24 | ||

| | |PIN_RXN_EP_1 | ||

| | |D85_SOC_PCIE_TX2P | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |N25 | ||

| | |PIN_RXP_EP_1 | ||

| | |D85_SOC_PCIE_TX2N | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

|- | |- | ||

| | |P1 | ||

| | |PIN_DQSB_CH3 | ||

| | |D90_NAND_CH3_DQS_N | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |- | ||

| | |P2 | ||

| | |PIN_DQS_CH3 | ||

| | |D90_NAND_CH3_DQS_P | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |- | ||

| | |P3 | ||

| | |PIN_AD_CH3[3] | ||

| | |S50_NAND_CH3_AD3 | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |- | ||

| | |P4 | ||

| | |PIN_AD_CH3[2] | ||

| | |S50_NAND_CH3_AD2 | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |- | ||

| | |P5 | ||

| | |PIN_AD_CH3[1] | ||

| | |S50_NAND_CH3_AD1 | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |- | ||

| | |P6 | ||

| | |PIN_AD_CH3[0] | ||

| | |S50_NAND_CH3_AD0 | ||

|[[File:Pin | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

|- | |- | ||

| | |P7 | ||

| | |VSS_P7 | ||

| | |GND | ||

|[[File:Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

|Y14 | |P8 | ||

|PIN_TEST[11] | |VSS_P8 | ||

| | |GND | ||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |||

|P9 | |||

|VDDOFIO_P9 | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|P10 | |||

|VDD_P10 | |||

|0.8V_FC_VDD | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|P11 | |||

|VDD_P11 | |||

|0.8V_FC_VDD | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|P12 | |||

|VSS_P12 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|P13 | |||

|VSS_P13 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|P14 | |||

|VDD_P14 | |||

|0.8V_FC_VDD | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|P15 | |||

|VDD_P15 | |||

|0.8V_FC_VDD | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|P16 | |||

|VSS_P16 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|P17 | |||

|AVDD18_PCIE_P17 | |||

|1.8V_FC_AVDD | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|P18 | |||

|VSS_P18 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|P19 | |||

|VSS_P19 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|P20 | |||

|VSS_P20 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|P21 | |||

|PIN_TXN_EP_1 | |||

|D85_SOC_PCIE_RX2P | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|P22 | |||

|PIN_TXP_EP_1 | |||

|D85_SOC_PCIE_RX2N | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|P23 | |||

|VSS_P23 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|P24 | |||

|VSS_P24 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|P25 | |||

|VSS_P25 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|R1 | |||

|PIN_REB_CH2 | |||

|D90_NAND_CH2_RE_ N S50_/ | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|R2 | |||

|PIN_RE_CH2 | |||

|D90_NAND_CH2_RE_ P | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|R3 | |||

|PIN_CE1_CH2 | |||

|S50_/NAND_CH2_CE1 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|R4 | |||

|PIN_CE0_CH2 | |||

|S50_/NAND_CH2_CE0 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|R5 | |||

|PIN_ALE_CH2 | |||

|S50_NAND_CH2_ALE | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|R6 | |||

|PIN_CLE_CH2 | |||

|S50_NAND_CH2_CLE | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|R7 | |||

|PIN_CE2_CH2 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|R8 | |||

|VSS_R8 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|R9 | |||

|VDDOFIO_R9 | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|R10 | |||

|VSS_R10 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|R11 | |||

|VSS_R11 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|R12 | |||

|VDD_R12 | |||

|0.8V_FC_VDD | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|R13 | |||

|VDD_R13 | |||

|0.8V_FC_VDD | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|R14 | |||

|VSS_R14 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|R15 | |||

|VSS_R15 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|R16 | |||

|VDD_R16 | |||

|0.8V_FC_VDD | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|R17 | |||

|AVDD18_PCIE_R17 | |||

|1.8V_FC_AVDD | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|R18 | |||

|VSS_R18 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|R19 | |||

|VSS_R19 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|R20 | |||

|VSS_R20 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|R21 | |||

|VSS_R21 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|R22 | |||

|VSS_R22 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|R23 | |||

|VSS_R23 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|R24 | |||

|PIN_RXN_EP_2 | |||

|D85_SOC_PCIE_TX1P | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|R25 | |||

|PIN_RXP_EP_2 | |||

|D85_SOC_PCIE_TX1N | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|T1 | |||

|PIN_AD_CH2[7] | |||

|S50_NAND_CH2_AD7 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|T2 | |||

|PIN_AD_CH2[6] | |||

|S50_NAND_CH2_AD6 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|T3 | |||

|VSS_T3 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|T4 | |||

|PIN_AD_CH2[5] | |||

|S50_NAND_CH2_AD5 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|T5 | |||

|PIN_AD_CH2[4] | |||

|S50_NAND_CH2_AD4 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|T6 | |||

|PIN_WE_CH2 | |||

|NAND_CH2_WE | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|T7 | |||

|PIN_CE3_CH2 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|T8 | |||

|VSS_T8 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|T9 | |||

|VDDOFIO_T9 | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|T10 | |||

|VDD_T10 | |||

|0.8V_FC_VDD | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|T11 | |||

|VDD_T11 | |||

|0.8V_FC_VDD | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|T12 | |||

|VSS_T12 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|T13 | |||

|VDDO_MISC | |||

|3.3V_FC_VDDQ_MISC | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|T14 | |||

|VDD_T14 | |||

|0.8V_FC_VDD | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|T15 | |||

|VDD_T15 | |||

|0.8V_FC_VDD | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|T16 | |||

|VSS_T16 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|T17 | |||

|PIN_ISET | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|T18 | |||

|VSS_T18 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|T19 | |||

|PIN_PERSTN | |||

|PCIE_PERSTN | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|T20 | |||

|VSS_T20 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|T21 | |||

|PIN_TXN_EP_2 | |||

|D85_SOC_PCIE_RX1P | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|T22 | |||

|PIN_TXP_EP_2 | |||

|D85_SOC_PCIE_RX1N | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|T23 | |||

|VSS_T23 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|T24 | |||

|VSS_T24 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|T25 | |||

|VSS_T25 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|U1 | |||

|PIN_DQSB_CH2 | |||

|D90_NAND_CH2_DQS_N | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|U2 | |||

|PIN_DQS_CH2 | |||

|D90_NAND_CH2_DQS_P | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|U3 | |||

|PIN_AD_CH2[3] | |||

|S50_NAND_CH2_AD3 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|U4 | |||

|PIN_AD_CH2[2] | |||

|S50_NAND_CH2_AD2 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|U5 | |||

|PIN_AD_CH2[1] | |||

|S50_NAND_CH2_AD1 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|U6 | |||

|PIN_AD_CH2[0] | |||

|S50_NAND_CH2_AD0 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|U7 | |||

|VSS_U7 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|U8 | |||

|VSS_U8 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|U9 | |||

|VSS_U9 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|U10 | |||

|VDDQMIO_U10 | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|U11 | |||

|VDDQMIO_U11 | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|U12 | |||

|VDDQMIO_U12 | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|U13 | |||

|AVDD18_PLLA | |||

|1.8V_FC_AVDD | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|U14 | |||

|VSS_U14 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|U15 | |||

|VDDO_MISC_1P8V | |||

|1.8V_FC_AVDD | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|U16 | |||

|AVDD18_EFUSE | |||

|1.8V_FC_AVDD | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|U17 | |||

|VSS_U17 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|U18 | |||

|AVDD18_ANA | |||

|1.8V_FC_AVDD | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|U19 | |||

|PIN_JT0_CLK | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|U20 | |||

|VSS_U20 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|U21 | |||

|VSS_U21 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|U22 | |||

|VSS_U22 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|U23 | |||

|VSS_U23 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|U24 | |||

|PIN_RXN_EP_3 | |||

|D85_SOC_PCIE_TX0P | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|U25 | |||

|PIN_RXP_EP_3 | |||

|D85_SOC_PCIE_TX0N | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|V1 | |||

|PIN_RE_CH1 | |||

|D90_NAND_CH1_RE_ P | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|V2 | |||

|PIN_REB_CH1 | |||

|D90_NAND_CH1_RE_ N S50_/ | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|V3 | |||

|PIN_CE1_CH1 | |||

|S50_/NAND_CH2_CE1 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|V4 | |||

|PIN_CE0_CH1 | |||

|S50_/NAND_CH2_CE0 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|V5 | |||

|PIN_ALE_CH1 | |||

|S50_NAND_CH1_ALE | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|V6 | |||

|PIN_CLE_CH1 | |||

|S50_NAND_CH1_CLE | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|V7 | |||

|VSS_V7 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|V8 | |||

|VSS_V8 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|V9 | |||

|VSS_V9 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|V10 | |||

|VDDQMIO_V10 | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|V11 | |||

|VDDQMIO_V11 | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|V12 | |||

|VDDQMIO_V12 | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|V13 | |||

|PIN_TEST[13] | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|V14 | |||

|PIN_TEST[8] | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|V15 | |||

|PIN_TEST[5] | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|V16 | |||

|PIN_TEST[7] | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|V17 | |||

|AVDD18_PLL | |||

|1.8V_FC_AVDD | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|V18 | |||

|PIN_TEST[0] | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|V19 | |||

|PIN_JT0_TMS | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|V20 | |||

|VSS_V20 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|V21 | |||

|PIN_TXN_EP_3 | |||

|D85_SOC_PCIE_RX0P | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|V22 | |||

|PIN_TXP_EP_3 | |||

|D85_SOC_PCIE_RX0N | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|V23 | |||

|VSS_V23 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|V24 | |||

|VSS_V24 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|V25 | |||

|VSS_V25 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|W1 | |||

|PIN_AD_CH1[7] | |||

|S50_NAND_CH1_AD7 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|W2 | |||

|PIN_AD_CH1[6] | |||

|S50_NAND_CH1_AD6 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|W3 | |||

|VSS_W3 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|W4 | |||

|PIN_AD_CH1[5] | |||

|S50_NAND_CH1_AD5 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|W5 | |||

|PIN_WE_CH1 | |||

|NAND_CH1_WE | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|W6 | |||

|PIN_CE2_CH1 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|W7 | |||

|PIN_CE3_CH1 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|W8 | |||

|VSS_W8 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|W9 | |||

|VSS_W9 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|W10 | |||

|VSS_W10 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|W11 | |||

|VSS_W11 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|W12 | |||

|PIN_TEST[15] | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|W13 | |||

|PIN_TEST[9] | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|W14 | |||

|PIN_TEST[3] | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|W15 | |||

|VSS_W15 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|W16 | |||

|PIN_TEST[12] | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|W17 | |||

|PIN_TEST[6] | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|W18 | |||

|PIN_TEST[1] | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|W19 | |||

|PIN_CTS | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|W20 | |||

|PIN_RTS | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|W21 | |||

|VSS_W21 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|W22 | |||

|VSS_W22 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|W23 | |||

|VSS_W23 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|W24 | |||

|PIN_RXN_RC0 | |||

|D85_FC_RX0N | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|W25 | |||

|PIN_RXP_RC0 | |||

|D85_FC_RX0P | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|Y1 | |||

|PIN_DQSB_CH1 | |||

|D90_NAND_CH1_DQS_ P | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|Y2 | |||

|PIN_DQS_CH1 | |||

|D90_NAND_CH1_DQS_ N | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|Y3 | |||

|PIN_AD_CH1[4] | |||

|S50_NAND_CH1_AD4 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|Y4 | |||

|PIN_AD_CH1[3] | |||

|S50_NAND_CH1_AD3 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|Y5 | |||

|PIN_AD_CH1[2] | |||

|S50_NAND_CH1_AD2 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|Y6 | |||

|VSS_Y6 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|Y7 | |||

|PIN_WP | |||

|S50_/NAND_WP | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|Y8 | |||

|VSS_Y8 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|Y9 | |||

|VSS_Y9 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|Y10 | |||

|VSS_Y10 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|Y11 | |||

|VSS_Y11 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|Y12 | |||

|VSS_Y12 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|Y13 | |||

|PIN_TEST[16] | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|Y14 | |||

|PIN_TEST[11] | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|Y15 | |||

|PIN_TEST[10] | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|Y16 | |||

|PIN_TEST[14] | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|Y17 | |||

|PIN_TEST[4] | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|Y18 | |||

|PIN_TEST[2] | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|Y19 | |||

|PIN_GPIO_0 | |||

|FC_MANU_MODE_SEL | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|Y20 | |||

|VSS_Y20 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|Y21 | |||

|PIN_TXN_RC0 | |||

|D85_FC_TX0N | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|Y22 | |||

|PIN_TXP_RC0 | |||

|D85_FC_TX0P | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |- | ||

| | |Y23 | ||

| | |VSS_Y23 | ||

| | |GND | ||

|[[File:Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |Y24 | ||

| | |VSS_Y24 | ||

| | |GND | ||

|[[File:Pin- | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |Ground | ||

|- | |- | ||

| | |Y25 | ||

| | |VSS_Y25 | ||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

| | |||

|[[File:IC-Pin- | |||

| | |||

|- | |- | ||

|} | |} | ||

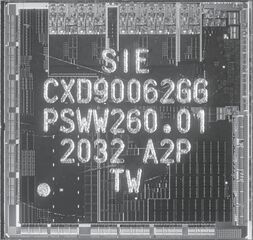

Revision as of 18:06, 13 December 2024

- NVME Controller, Codename Titania

Pinout

Pictures

Sources

https://www.flickr.com/photos/130561288@N04/albums/72157718290760702