CXD90062GG: Difference between revisions

Jump to navigation

Jump to search

(→Pinout: Added PIN_AD to all channels) |

(→Pinout: Added PIN_DQS/B to all channels) |

||

| Line 11: | Line 11: | ||

!Type | !Type | ||

!Description | !Description | ||

|- | |||

|A6 | |||

|PIN_DQSB_CH7 | |||

|D90_NAND_CH7_DQS_N | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |- | ||

|A9 | |A9 | ||

|PIN_AD_CH8[1] | |PIN_AD_CH8[1] | ||

|S50_NAND_CH8_AD1 | |S50_NAND_CH8_AD1 | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|A10 | |||

|PIN_DQS_CH8 | |||

|D90_NAND_CH8_DQS_P | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

| Line 21: | Line 33: | ||

|PIN_AD_CH8[7] | |PIN_AD_CH8[7] | ||

|S50_NAND_CH8_AD7 | |S50_NAND_CH8_AD7 | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|A13 | |||

|PIN_DQS_CH9 | |||

|D90_NAND_CH9_DQS_P | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

| Line 27: | Line 45: | ||

|PIN_AD_CH9[7] | |PIN_AD_CH9[7] | ||

|S50_NAND_CH9_AD7 | |S50_NAND_CH9_AD7 | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|A16 | |||

|PIN_DQSB_CH10 | |||

|D90_NAND_CH10_DQS_N | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

| Line 39: | Line 63: | ||

|PIN_AD_CH11[0] | |PIN_AD_CH11[0] | ||

|S50_NAND_CH11_AD0 | |S50_NAND_CH11_AD0 | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|A20 | |||

|PIN_DQSB_CH11 | |||

|D90_NAND_CH11_DQS_N | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

| Line 627: | Line 657: | ||

|PIN_AD_CH7[0] | |PIN_AD_CH7[0] | ||

|S50_NAND_CH7_AD0 | |S50_NAND_CH7_AD0 | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|B6 | |||

|PIN_DQS_CH7 | |||

|D90_NAND_CH7_DQS_P | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

| Line 639: | Line 675: | ||

|PIN_AD_CH8[0] | |PIN_AD_CH8[0] | ||

|S50_NAND_CH8_AD0 | |S50_NAND_CH8_AD0 | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|B10 | |||

|PIN_DQSB_CH8 | |||

|D90_NAND_CH8_DQS_N | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

| Line 645: | Line 687: | ||

|PIN_AD_CH8[6] | |PIN_AD_CH8[6] | ||

|S50_NAND_CH8_AD6 | |S50_NAND_CH8_AD6 | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|B13 | |||

|PIN_DQSB_CH9 | |||

|D90_NAND_CH9_DQS_N | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

| Line 651: | Line 699: | ||

|PIN_AD_CH9[6] | |PIN_AD_CH9[6] | ||

|S50_NAND_CH9_AD6 | |S50_NAND_CH9_AD6 | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|B16 | |||

|PIN_DQS_CH10 | |||

|D90_NAND_CH10_DQS_P | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

| Line 663: | Line 717: | ||

|PIN_AD_CH11[1] | |PIN_AD_CH11[1] | ||

|S50_NAND_CH11_AD1 | |S50_NAND_CH11_AD1 | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|B20 | |||

|PIN_DQS_CH11 | |||

|D90_NAND_CH11_DQS_P | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

| Line 669: | Line 729: | ||

|PIN_AD_CH11[7] | |PIN_AD_CH11[7] | ||

|S50_NAND_CH11_AD7 | |S50_NAND_CH11_AD7 | ||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|C1 | |||

|PIN_DQSB_CH6 | |||

|D90_NAND_CH6_DQS_N | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|C2 | |||

|PIN_DQS_CH6 | |||

|D90_NAND_CH6_DQS_P | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |[[File:IC-Pin-Out.png|alt=Others|frameless]] | ||

| | | | ||

| Line 916: | Line 988: | ||

|D85_M2_PCIE_TX1P | |D85_M2_PCIE_TX1P | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | |||

|- | |||

|G1 | |||

|PIN_DQS_CH5 | |||

|D90_NAND_CH5_DQS_P | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|G2 | |||

|PIN_DQSB_CH5 | |||

|D90_NAND_CH5_DQS_N | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | | | ||

|- | |- | ||

| Line 1,030: | Line 1,114: | ||

|D85_M2_PCIE_TX3P | |D85_M2_PCIE_TX3P | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | |||

|- | |||

|L1 | |||

|PIN_DQS_CH4 | |||

|D90_NAND_CH4_DQS_P | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|L2 | |||

|PIN_DQSB_CH4 | |||

|D90_NAND_CH4_DQS_N | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | | | ||

|- | |- | ||

| Line 1,126: | Line 1,222: | ||

|D85_SOC_PCIE_TX2N | |D85_SOC_PCIE_TX2N | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |||

|- | |||

|P1 | |||

|PIN_DQSB_CH3 | |||

|D90_NAND_CH3_DQS_N | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|P2 | |||

|PIN_DQS_CH3 | |||

|D90_NAND_CH3_DQS_P | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | | | ||

|- | |- | ||

| Line 1,222: | Line 1,330: | ||

|D85_SOC_PCIE_RX1N | |D85_SOC_PCIE_RX1N | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | |||

|- | |||

|U1 | |||

|PIN_DQSB_CH2 | |||

|D90_NAND_CH2_DQS_N | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|U2 | |||

|PIN_DQS_CH2 | |||

|D90_NAND_CH2_DQS_P | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | | | ||

|- | |- | ||

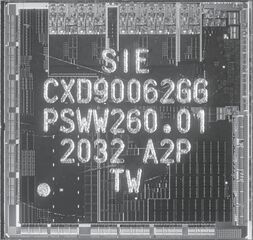

Revision as of 14:08, 13 December 2024

- NVME Controller, Codename Titania

Pinout

| Pad | Internal Name | External Name | Type | Description |

|---|---|---|---|---|

| A6 | PIN_DQSB_CH7 | D90_NAND_CH7_DQS_N | ||

| A9 | PIN_AD_CH8[1] | S50_NAND_CH8_AD1 | ||

| A10 | PIN_DQS_CH8 | D90_NAND_CH8_DQS_P | ||

| A11 | PIN_AD_CH8[7] | S50_NAND_CH8_AD7 | ||

| A13 | PIN_DQS_CH9 | D90_NAND_CH9_DQS_P | ||

| A14 | PIN_AD_CH9[7] | S50_NAND_CH9_AD7 | ||

| A16 | PIN_DQSB_CH10 | D90_NAND_CH10_DQS_N | ||

| A17 | PIN_AD_CH10[4] | S50_NAND_CH10_AD4 | ||

| A19 | PIN_AD_CH11[0] | S50_NAND_CH11_AD0 | ||

| A20 | PIN_DQSB_CH11 | D90_NAND_CH11_DQS_N | ||

| A21 | PIN_AD_CH11[6] | S50_NAND_CH11_AD6 | ||

| A5 | PIN_AD_CH7[1] | S50_NAND_CH7_AD1 | ||

| A7 | PIN_AD_CH7[7] | S50_NAND_CH7_AD7 | ||

| AA1 | PIN_AD_CH1[1] | S50_NAND_CH1_AD1 | ||

| AA2 | PIN_AD_CH1[0] | S50_NAND_CH1_AD0 | ||

| AA4 | PIN_CLE_CH0 | S50_NAND_CH0_CLE | ||

| AA5 | PIN_CE2_CH0 | |||

| AA6 | PIN_CE3_CH0 | |||

| AA12 | PIN_VREFSMIO | 1.2V_FC_VDDQMIO | ||

| AA14 | PIN_GPIO_7 | |||

| AA15 | PIN_SOC_V_RST | /FC_RESET | ||

| AA16 | PIN_GPIO_6 | PCIE_PEDET | ||

| AA17 | PIN_GPIO_5 | 3.3V_FC_VDDQ_MISC | ||

| AA18 | PIN_GPIO_4 | 3.3V_FC_VDDQ_MISC | ||

| AA19 | PIN_GPIO_2 | |||

| AA20 | PIN_F_CS_N | /FC_SPI_CS | ||

| AA24 | PIN_REFCLK_P_0 | D100G_FC_PCIE_CLK_P | ||

| AA25 | PIN_REFCLK_N_0 | D100G_FC_PCIE_CLK_N | ||

| AB1 | PIN_CE1_CH0 | S50_/NAND_CH2_CE1 | ||

| AB2 | PIN_CE0_CH0 | S50_/NAND_CH2_CE0 | ||

| AB3 | PIN_ALE_CH0 | S50_NAND_CH0_ALE | ||

| AB4 | PIN_AD_CH0[5] | S50_NAND_CH0_AD5 | ||

| AB5 | PIN_AD_CH0[3] | S50_NAND_CH0_AD3 | ||

| AB7 | PIN_M_A[15] | S50_FC_DDR_A15 | ||

| AB8 | PIN_M_A[11] | S50_FC_DDR_A11 | ||

| AB9 | PIN_M_A[8] | S50_FC_DDR_A8 | ||

| AB10 | PIN_M_A[4] | S50_FC_DDR_A4 | ||

| AB11 | PIN_M_ALERT_N | S50_/FC_DDR_ALERTN | ||

| AB12 | PIN_DDR_CAL | GND | Ground | |

| AB13 | PIN_M_ODT[0] | S50_FC_DDR_ODT0 | ||

| AB14 | PIN_M_CS_N[0] | S50_FC_DDR_CS0N | ||

| AB15 | PIN_M_D[7] | S50_FC_DDR_D7 | ||

| AB16 | PIN_M_D[6] | S50_FC_DDR_D6 | ||

| AB17 | PIN_M_D[2] | S50_FC_DDR_D2 | ||

| AB18 | PIN_M_D[1] | S50_FC_DDR_D1 | ||

| AB19 | PIN_M_DM | S50_FC_DDR_DM | ||

| AB20 | PIN_GPIO_1 | FC_BOOT_CPU_SEL | ||

| AB21 | PIN_F_Q | SSB_SPIM_MISO | ||

| AB22 | PIN_JT0_DI | |||

| AC1 | PIN_REB_CH0 | D90_NAND_CH0_RE_ N S50_/ | ||

| AC2 | PIN_RE_CH0 | D90_NAND_CH0_RE_P | ||

| AC4 | PIN_AD_CH0[4] | S50_NAND_CH0_AD4 | ||

| AC5 | PIN_AD_CH0[2] | S50_NAND_CH0_AD2 | ||

| AC7 | PIN_M_A[14] | S50_FC_DDR_A14 | ||

| AC9 | PIN_M_A[7] | S50_FC_DDR_A7 | ||

| AC10 | PIN_M_A[3] | S50_FC_DDR_A3 | ||

| AC12 | PIN_M_PAR | S50_FC_DDR_PAR | ||

| AC14 | PIN_M_CS_N[1] | N/C | No Connection | |

| AC15 | PIN_M_WE_N | S50_FC_DDR_WEN | ||

| AC17 | PIN_M_D[3] | S50_FC_DDR_D3 | ||

| AC19 | PIN_M_D[0] | S50_FC_DDR_D0 | ||

| AC20 | PIN_GPIO_3 | |||

| AC21 | PIN_F_SPI_INT | /FC_SPI_S_INT | ||

| AC22 | PIN_JT0_TRSTN | |||

| AC24 | PIN_XTLOUT | |||

| AC25 | PIN_XTLIN | S50G_FC_SYSCLK | ||

| AD2 | PIN_WE_CH0 | S50_NANO_CH0_WE | ||

| AD3 | PIN_AD_CH0[7] | S50_NAND_CH0_AD7 | ||

| AD4 | PIN_DQSB_CH0 | D90_NAND_CH0_DQS_N | ||

| AD5 | PIN_AD_CH0[0] | S50_NAND_CH0_AD0 | ||

| AD7 | PIN_M_A[13] | S50_FC_DDR_A13 | ||

| AD8 | PIN_M_A[9] | S50_FC_DDR_A9 | ||

| AD9 | PIN_M_A[6] | S50_FC_DDR_A6 | ||

| AD10 | PIN_M_A[2] | S50_FC_DDR_A2 | ||

| AD11 | PIN_M_BA[2] | S50_FC_DDR_BA2 | ||

| AD12 | PIN_M_BA[0] | S50_FC_DDR_BA0 | ||

| AD13 | PIN_M_ODT[1] | N/C | No Connection | |

| AD14 | PIN_M_CKE[0] | S50_FC_DDR_CKE0 | ||

| AD15 | PIN_M_CAS_N | S50_/FC_DDR_CASN | ||

| AD16 | PIN_M_CLOCK[0] | D90_FC_DDR_CLOCK0_P | ||

| AD17 | PIN_M_D[4] | S50_FC_DDR_D4 | ||

| AD18 | PIN_M_DQS_P[0] | D90_FC_DDR_DQS0_P | ||

| AD20 | PIN_RX2 | FC_UART2_RX | ||

| AD21 | PIN_TX | FC_UART1_TX | ||

| AD22 | PIN_F_D | SSB_SPIM_MOSI | ||

| AD23 | PIN_CLK_REQ_N_0 | /FC_CLK_REQ_N | ||

| AD24 | PIN_ANA_TP | |||

| AE3 | PIN_AD_CH0[6] | S50_NAND_CH0_AD6 | ||

| AE4 | PIN_DQS_CH0 | D90_NAND_CH0_DQS_P | ||

| AE5 | PIN_AD_CH0[1] | S50_NAND_CH0_AD1 | ||

| AE7 | PIN_M_A[12] | S50_FC_DDR_A12 | ||

| AE8 | PIN_M_A[10] | S50_FC_DDR_A10 | ||

| AE9 | PIN_M_A[5] | S50_FC_DDR_A5 | ||

| AE10 | PIN_M_A[1] | S50_FC_DDR_A1 | ||

| AE11 | PIN_M_A[0] | S50_FC_DDR_A0 | ||

| AE12 | PIN_M_BA[1] | S50_FC_DDR_BA1 | ||

| AE13 | PIN_M_RST_N | NS50_/FC_DDR_RSTN | ||

| AE14 | PIN_M_CKE[1] | GND | Ground | |

| AE15 | PIN_M_RAS_N | S50_/FC_DDR_RASN | ||

| AE16 | PIN_M_CLOCK_N[0] | D90_FC_DDR_CLOCK0_N | ||

| AE17 | PIN_M_D[5] | S50_FC_DDR_D5 | ||

| AE18 | PIN_M_DQS_N[0] | D90_FC_DDR_DQS0_N | ||

| AE20 | PIN_TX2 | FC_UART2_TX | ||

| AE21 | PIN_RX | FC_UART1_RX | ||

| AE22 | PIN_F_CLK | SSB_SPIM_CLK | ||

| AE23 | PIN_JT0_DO | |||

| B2 | PIN_AD_CH6[6] | S50_NAND_CH6_AD6 | ||

| B5 | PIN_AD_CH7[0] | S50_NAND_CH7_AD0 | ||

| B6 | PIN_DQS_CH7 | D90_NAND_CH7_DQS_P | ||

| B7 | PIN_AD_CH7[6] | S50_NAND_CH7_AD6 | ||

| B9 | PIN_AD_CH8[0] | S50_NAND_CH8_AD0 | ||

| B10 | PIN_DQSB_CH8 | D90_NAND_CH8_DQS_N | ||

| B11 | PIN_AD_CH8[6] | S50_NAND_CH8_AD6 | ||

| B13 | PIN_DQSB_CH9 | D90_NAND_CH9_DQS_N | ||

| B14 | PIN_AD_CH9[6] | S50_NAND_CH9_AD6 | ||

| B16 | PIN_DQS_CH10 | D90_NAND_CH10_DQS_P | ||

| B17 | PIN_AD_CH10[5] | S50_NAND_CH10_AD5 | ||

| B19 | PIN_AD_CH11[1] | S50_NAND_CH11_AD1 | ||

| B20 | PIN_DQS_CH11 | D90_NAND_CH11_DQS_P | ||

| B21 | PIN_AD_CH11[7] | S50_NAND_CH11_AD7 | ||

| C1 | PIN_DQSB_CH6 | D90_NAND_CH6_DQS_N | ||

| C2 | PIN_DQS_CH6 | D90_NAND_CH6_DQS_P | ||

| C4 | PIN_AD_CH6[7] | S50_NAND_CH6_AD7 | ||

| C7 | PIN_AD_CH7[5] | S50_NAND_CH7_AD5 | ||

| C10 | PIN_AD_CH8[4] | S50_NAND_CH8_AD4 | ||

| C13 | PIN_AD_CH9[3] | S50_NAND_CH9_AD3 | ||

| C16 | PIN_AD_CH10[0] | S50_NAND_CH10_AD0 | ||

| C19 | PIN_AD_CH11[2] | S50_NAND_CH11_AD2 | ||

| C24 | PIN_RXN_RC1_0 | D85_M2_PCIE_RX0N | ||

| C25 | PIN_RXP_RC1_0 | D85_M2_PCIE_RX0P | ||

| D1 | PIN_AD_CH6[3] | S50_NAND_CH6_AD3 | ||

| D2 | PIN_AD_CH6[2] | S50_NAND_CH6_AD2 | ||

| D3 | PIN_AD_CH6[5] | S50_NAND_CH6_AD5 | ||

| D4 | PIN_AD_CH6[4] | S50_NAND_CH6_AD4 | ||

| D6 | PIN_AD_CH7[2] | S50_NAND_CH7_AD2 | ||

| D7 | PIN_AD_CH7[4] | S50_NAND_CH7_AD4 | ||

| D10 | PIN_AD_CH8[3] | S50_NAND_CH8_AD3 | ||

| D11 | PIN_AD_CH8[5] | S50_NAND_CH8_AD5 | ||

| D13 | PIN_AD_CH9[2] | S50_NAND_CH9_AD2 | ||

| D14 | PIN_AD_CH9[5] | S50_NAND_CH9_AD5 | ||

| D16 | PIN_AD_CH10[1] | S50_NAND_CH10_AD1 | ||

| D17 | PIN_AD_CH10[6] | S50_NAND_CH10_AD6 | ||

| D19 | PIN_AD_CH11[3] | S50_NAND_CH11_AD3 | ||

| D21 | PIN_TXN_RC1_0 | D85_M2_PCIE_TX0N | ||

| D22 | PIN_TXP_RC1_0 | D85_M2_PCIE_TX0P | ||

| E4 | PIN_AD_CH6[1] | S50_NAND_CH6_AD1 | ||

| E5 | PIN_AD_CH6[0] | S50_NAND_CH6_AD0 | ||

| E7 | PIN_AD_CH7[3] | S50_NAND_CH7_AD3 | ||

| E10 | PIN_AD_CH8[2] | S50_NAND_CH8_AD2 | ||

| E13 | PIN_AD_CH9[1] | S50_NAND_CH9_AD1 | ||

| E14 | PIN_AD_CH9[4] | S50_NAND_CH9_AD4 | ||

| E16 | PIN_AD_CH10[2] | S50_NAND_CH10_AD2 | ||

| E17 | PIN_AD_CH10[7] | S50_NAND_CH10_AD7 | ||

| E19 | PIN_AD_CH11[5] | S50_NAND_CH11_AD5 | ||

| E24 | PIN_RXN_RC1_1 | D85_M2_PCIE_RX1N | ||

| E25 | PIN_RXP_RC1_1 | D85_M2_PCIE_RX1P | ||

| F1 | PIN_AD_CH5[4] | S50_NAND_CH5_AD4 | ||

| F2 | PIN_AD_CH5[5] | S50_NAND_CH5_AD5 | ||

| F13 | PIN_AD_CH9[0] | S50_NAND_CH9_AD0 | ||

| F16 | PIN_AD_CH10[3] | S50_NAND_CH10_AD3 | ||

| F19 | PIN_AD_CH11[4] | S50_NAND_CH11_AD4 | ||

| F21 | PIN_TXN_RC1_1 | D85_M2_PCIE_TX1N | ||

| F22 | PIN_TXP_RC1_1 | D85_M2_PCIE_TX1P | ||

| G1 | PIN_DQS_CH5 | D90_NAND_CH5_DQS_P | ||

| G2 | PIN_DQSB_CH5 | D90_NAND_CH5_DQS_N | ||

| G4 | PIN_AD_CH5[7] | S50_NAND_CH5_AD7 | ||

| G3 | PIN_AD_CH5[6] | S50_NAND_CH5_AD6 | ||

| G24 | PIN_RXN_RC1_2 | D85_M2_PCIE_RX2N | ||

| G25 | PIN_RXP_RC1_2 | D85_M2_PCIE_RX2P | ||

| H1 | PIN_AD_CH5[0] | S50_NAND_CH5_AD0 | ||

| H2 | PIN_AD_CH5[1] | S50_NAND_CH5_AD1 | ||

| H4 | PIN_AD_CH5[2] | S50_NAND_CH5_AD2 | ||

| H5 | PIN_AD_CH5[3] | S50_NAND_CH5_AD3 | ||

| H13 | PIN_VREF_NF[1] | 1.2V_FC_VDDQFIO | ||

| H21 | PIN_TXN_RC1_2 | D85_M2_PCIE_TX2N | ||

| H22 | PIN_TXP_RC1_2 | D85_M2_PCIE_TX2P | ||

| J24 | PIN_RXN_RC1_3 | D85_M2_PCIE_RX3N | ||

| J25 | PIN_RXP_RC1_3 | D85_M2_PCIE_RX3P | ||

| K1 | PIN_AD_CH4[4] | S50_NAND_CH4_AD4 | ||

| K2 | PIN_AD_CH4[5] | S50_NAND_CH4_AD5 | ||

| K4 | PIN_AD_CH4[6] | S50_NAND_CH4_AD6 | ||

| K5 | PIN_AD_CH4[7] | S50_NAND_CH4_AD7 | ||

| K21 | PIN_TXN_RC1_3 | D85_M2_PCIE_TX3N | ||

| K22 | PIN_TXP_RC1_3 | D85_M2_PCIE_TX3P | ||

| L1 | PIN_DQS_CH4 | D90_NAND_CH4_DQS_P | ||

| L2 | PIN_DQSB_CH4 | D90_NAND_CH4_DQS_N | ||

| L3 | PIN_AD_CH4[3] | S50_NAND_CH4_AD3 | ||

| L4 | PIN_AD_CH4[2] | S50_NAND_CH4_AD2 | ||

| L5 | PIN_AD_CH4[1] | S50_NAND_CH4_AD1 | ||

| L6 | PIN_AD_CH4[0] | S50_NAND_CH4_AD0 | ||

| L24 | PIN_RXN_EP_0 | D85_SOC_PCIE_TX3P | ||

| L25 | PIN_RXP_EP_0 | D85_SOC_PCIE_TX3N | ||

| M8 | PIN_CAL_NF | S50_/NAND_WP | ||

| M21 | PIN_TXN_EP_0 | D85_SOC_PCIE_RX3P | ||

| M22 | PIN_TXP_EP_0 | D85_SOC_PCIE_RX3N | ||

| N1 | PIN_AD_CH3[7] | S50_NAND_CH3_AD7 | ||

| N2 | PIN_AD_CH3[6] | S50_NAND_CH3_AD6 | ||

| N3 | PIN_AD_CH3[5] | S50_NAND_CH3_AD5 | ||

| N4 | PIN_AD_CH3[4] | S50_NAND_CH3_AD4 | ||

| N8 | PIN_VREF_NF[0] | 1.2V_FC_VDDQFIO | ||

| N24 | PIN_RXN_EP_1 | D85_SOC_PCIE_TX2P | ||

| N25 | PIN_RXP_EP_1 | D85_SOC_PCIE_TX2N | ||

| P1 | PIN_DQSB_CH3 | D90_NAND_CH3_DQS_N | ||

| P2 | PIN_DQS_CH3 | D90_NAND_CH3_DQS_P | ||

| P3 | PIN_AD_CH3[3] | S50_NAND_CH3_AD3 | ||

| P4 | PIN_AD_CH3[2] | S50_NAND_CH3_AD2 | ||

| P5 | PIN_AD_CH3[1] | S50_NAND_CH3_AD1 | ||

| P6 | PIN_AD_CH3[0] | S50_NAND_CH3_AD0 | ||

| P21 | PIN_TXN_EP_1 | D85_SOC_PCIE_RX2P | ||

| P22 | PIN_TXP_EP_1 | D85_SOC_PCIE_RX2N | ||

| R24 | PIN_RXN_EP_2 | D85_SOC_PCIE_TX1P | ||

| R25 | PIN_RXP_EP_2 | D85_SOC_PCIE_TX1N | ||

| T1 | PIN_AD_CH2[7] | S50_NAND_CH2_AD7 | ||

| T2 | PIN_AD_CH2[6] | S50_NAND_CH2_AD6 | ||

| T4 | PIN_AD_CH2[5] | S50_NAND_CH2_AD5 | ||

| T5 | PIN_AD_CH2[4] | S50_NAND_CH2_AD4 | ||

| T17 | PIN_ISET | GND | Ground | |

| T19 | PIN_PERSTN | PCIE_PERSTN | ||

| T21 | PIN_TXN_EP_2 | D85_SOC_PCIE_RX1P | ||

| T22 | PIN_TXP_EP_2 | D85_SOC_PCIE_RX1N | ||

| U1 | PIN_DQSB_CH2 | D90_NAND_CH2_DQS_N | ||

| U2 | PIN_DQS_CH2 | D90_NAND_CH2_DQS_P | ||

| U3 | PIN_AD_CH2[3] | S50_NAND_CH2_AD3 | ||

| U4 | PIN_AD_CH2[2] | S50_NAND_CH2_AD2 | ||

| U5 | PIN_AD_CH2[1] | S50_NAND_CH2_AD1 | ||

| U6 | PIN_AD_CH2[0] | S50_NAND_CH2_AD0 | ||

| U19 | PIN_JT0_CLK | |||

| U24 | PIN_RXN_EP_3 | D85_SOC_PCIE_TX0P | ||

| U25 | PIN_RXP_EP_3 | D85_SOC_PCIE_TX0N | ||

| V1 | PIN_RE_CH1 | D90_NAND_CH1_RE_ P | ||

| V2 | PIN_REB_CH1 | D90_NAND_CH1_RE_ N S50_/ | ||

| V3 | PIN_CE1_CH1 | S50_/NAND_CH2_CE1 | ||

| V4 | PIN_CE0_CH1 | S50_/NAND_CH2_CE0 | ||

| V5 | PIN_ALE_CH1 | S50_NAND_CH1_ALE | ||

| V6 | PIN_CLE_CH1 | S50_NAND_CH1_CLE | ||

| V18 | PIN_TEST[0] | |||

| V13 | PIN_TEST[13] | |||

| V14 | PIN_TEST[8] | |||

| V15 | PIN_TEST[5] | |||

| V16 | PIN_TEST[7] | |||

| V19 | PIN_JT0_TMS | |||

| V21 | PIN_TXN_EP_3 | D85_SOC_PCIE_RX0P | ||

| V22 | PIN_TXP_EP_3 | D85_SOC_PCIE_RX0N | ||

| W1 | PIN_AD_CH1[7] | S50_NAND_CH1_AD7 | ||

| W2 | PIN_AD_CH1[6] | S50_NAND_CH1_AD6 | ||

| W4 | PIN_AD_CH1[5] | S50_NAND_CH1_AD5 | ||

| W5 | PIN_WE_CH1 | NAND_CH1_WE | ||

| W6 | PIN_CE2_CH1 | |||

| W7 | PIN_CE3_CH1 | |||

| W12 | PIN_TEST[15] | |||

| W13 | PIN_TEST[9] | |||

| W14 | PIN_TEST[3] | |||

| W16 | PIN_TEST[12] | |||

| W17 | PIN_TEST[6] | |||

| W18 | PIN_TEST[1] | |||

| W19 | PIN_CTS | GND | Ground | |

| W20 | PIN_RTS | |||

| W24 | PIN_RXN_RC0 | D85_FC_RX0N | ||

| W25 | PIN_RXP_RC0 | D85_FC_RX0P | ||

| Y1 | PIN_DQSB_CH1 | D90_NAND_CH1_DQS_ P | ||

| Y2 | PIN_DQS_CH1 | D90_NAND_CH1_DQS_ N | ||

| Y3 | PIN_AD_CH1[4] | S50_NAND_CH1_AD4 | ||

| Y4 | PIN_AD_CH1[3] | S50_NAND_CH1_AD3 | ||

| Y5 | PIN_AD_CH1[2] | S50_NAND_CH1_AD2 | ||

| Y7 | PIN_WP | S50_/NAND_WP | ||

| Y13 | PIN_TEST[16] | |||

| Y14 | PIN_TEST[11] | |||

| Y15 | PIN_TEST[10] | |||

| Y16 | PIN_TEST[14] | |||

| Y17 | PIN_TEST[4] | |||

| Y19 | PIN_GPIO_0 | FC_MANU_MODE_SEL | ||

| Y21 | PIN_TXN_RC0 | D85_FC_TX0N | ||

| Y18 | PIN_TEST[2] | |||

| Y22 | PIN_TXP_RC0 | D85_FC_TX0P |

Pictures

Sources

https://www.flickr.com/photos/130561288@N04/albums/72157718290760702