XDPE14286A: Difference between revisions

Jump to navigation

Jump to search

(→Pinout: Added XDPE14286A) |

|||

| (One intermediate revision by one other user not shown) | |||

| Line 1: | Line 1: | ||

= Pinout = | |||

{| class="wikitable mw-collapsible" | |||

|+ | |||

!Pad | |||

!Internal Name | |||

!External Name | |||

!Type | |||

!Description | |||

|- | |||

|1 | |||

|PWM8_1 | |||

|5V_MAIN | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|2 | |||

|PWM7_2 | |||

|5V_MAIN | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|3 | |||

|PWM6_3 | |||

|5V_MAIN | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|4 | |||

|PWM5_4 | |||

|5V_MAIN | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|5 | |||

|PWM4 | |||

|5V_MAIN | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|6 | |||

|PWM3 | |||

|5V_MAIN | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|7 | |||

|PWM2 | |||

|5V_MAIN | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|8 | |||

|PWM1 | |||

|5V_MAIN | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|9 | |||

|SDA | |||

|SOC_I2C_SDA | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|10 | |||

|SCL | |||

|SOC_I2C_SCL | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|11 | |||

|/MP_SMBALERT | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|12 | |||

|AVRRDY | |||

|/VDDNB_VRM_POWFAIL | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|13 | |||

|AVREN | |||

|PSW_MSOC_PGC | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|14 | |||

|/VRHOT | |||

|/SOC_VRM_HOT | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|15 | |||

|\MP_PINALRT | |||

|/SOC_GPU_PCC | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|16 | |||

|MP_BVRRDY | |||

|/VDD_VRM_POW_FAIL | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|17 | |||

|/MP_BVREN_NVLP | |||

|PSW_MSOC_PGC | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|18 | |||

|PWROK_NVPWMVID | |||

|SOC_PWROK | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|19 | |||

|VDDIO | |||

|1.8V_SOC_VDDA | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|20 | |||

|SVC_NVPSI | |||

|S50_SOC_SVI2_SCL | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|21 | |||

|SVD_NVSTDBY | |||

|S50_SOC_SVI2_SDA | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|22 | |||

|SVT | |||

|S50_SOC_SVI2_SVT | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|23 | |||

|VCLK | |||

|3.3V_VRM | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|24 | |||

|VDIO | |||

|3.3V_VRM | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|25 | |||

|/VALRT | |||

|3.3V_VRM | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|26 | |||

|MP_IMON | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|27 | |||

|AVSEN | |||

|VDDCR_GFX_SENSE | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|28 | |||

|AVREF | |||

|SOC_VSS_SENSE1 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|29 | |||

|IREF1 | |||

|1.0V_SOC_VGFX | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|30 | |||

|ISEN1 | |||

|ISEN1 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|31 | |||

|IREF2 | |||

|1.0V_SOC_VGFX | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|32 | |||

|ISEN2 | |||

|ISEN2 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|33 | |||

|IREF3 | |||

|1.0V_SOC_VGFX | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|34 | |||

|ISEN3 | |||

|ISEN3 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|35 | |||

|IREF4 | |||

|1.0V_SOC_VGFX | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|36 | |||

|ISEN4 | |||

|ISEN4 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|37 | |||

|IREF5_4 | |||

|1.0V_SOC_VGFX | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|38 | |||

|ISEN5_4 | |||

|ISEN5_4 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|39 | |||

|IREF6_3 | |||

|1.0V_SOC_VGFX | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|40 | |||

|ISEN6_3 | |||

|ISEN6_3 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|41 | |||

|IREF7_2 | |||

|1.0V_SOC_VGFX | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|42 | |||

|ISEN7_2 | |||

|ISEN7_2 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|43 | |||

|IREF8_1 | |||

|1.0V_SOC_VGFX | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|44 | |||

|ISEN8_1 | |||

|ISEN8_1 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|45 | |||

|BVREF | |||

|SOC_VSS_SENSE1 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|46 | |||

|BVSEN | |||

|VDDCR_CORE_SENSE | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|47 | |||

|MP_FAULT2 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|48 | |||

|MP_FAULT1 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|49 | |||

|XADDR2 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|50 | |||

|TSEN1 | |||

|VGFX TEMP. | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|51 | |||

|TSEN2_IINSEN_VAUX | |||

|VCORE TEMP. | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|52 | |||

|XADDR1 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|53 | |||

|PSYSP_IINSEN_VAUX_VSYS | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|54 | |||

|PSYSN_VINSEN | |||

|12V_MAIN | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|55 | |||

|VDD | |||

|3.3V_VRM | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|56 | |||

|VD12 | |||

|1.2V_VRM | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|57 | |||

| | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|} | |||

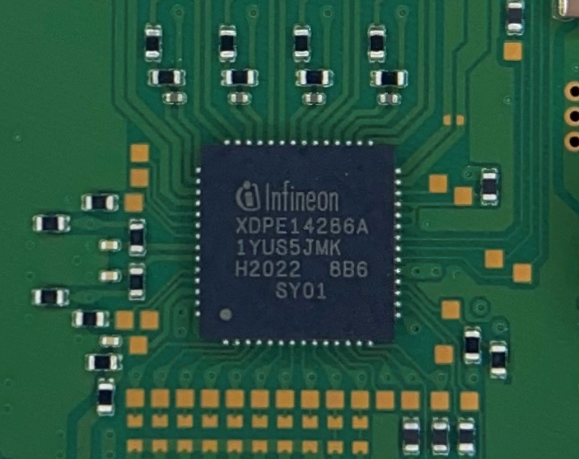

= Pictures = | = Pictures = | ||

[[File:XDPE14286A.png]] | [[File:XDPE14286A.png]] | ||

[[File:Infineon_XDPE14286A_Proto.png]] | |||