TH58LJT0T24BA4M: Difference between revisions

Jump to navigation

Jump to search

(→Pinout: Added TH58LJT0T24BA4M) |

|||

| (One intermediate revision by one other user not shown) | |||

| Line 1: | Line 1: | ||

= Pinout = | |||

There are six chips, each with identical inputs but assigned to different channels. | |||

The first chip operates on channels 0 and 1, the second on channels 2 and 3, and so forth. | |||

{| class="wikitable mw-collapsible" | |||

|+ | |||

!Pad | |||

!Internal Name | |||

!External Name | |||

!Type | |||

!Description | |||

|- | |||

|A1 | |||

|NC_A1 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|A2 | |||

|NC_A2 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|A3 | |||

|NC_A3 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|A4 | |||

|NC_A4 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|A10 | |||

|NC_A10 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|A11 | |||

|NC_A11 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|A12 | |||

|NC_A12 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|A13 | |||

|NC_A13 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|B1 | |||

|NC_B1 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|B2 | |||

|NC_B2 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|B3 | |||

|NC_B3 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|B4 | |||

|NC_B4 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|B10 | |||

|NC_B10 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|B11 | |||

|NC_B11 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|B12 | |||

|NC_B12 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|B13 | |||

|NC_B13 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|C1 | |||

|NU_C1 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|C2 | |||

|NU_C2 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|C3 | |||

|NU_C3 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|C4 | |||

|NU_C4 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|C10 | |||

|NU_C10 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|C11 | |||

|NU_C11 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|C12 | |||

|NU_C12 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|C13 | |||

|NU_C13 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|D1 | |||

|NU_D1 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|D2 | |||

|NU_D2 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|D3 | |||

|VCCQ_D3 | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|D4 | |||

|VCCQ_D4 | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|D5 | |||

|DQ1[3] | |||

|S50_NAND_CH0_AD3 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|D6 | |||

|VSS_D6 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|D8 | |||

|VCC_D8 | |||

|2.5V_NAND_VCC | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|D9 | |||

|DQ1[4] | |||

|S50_NAND_CH0_AD4 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|D10 | |||

|VCCQ_D10 | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|D11 | |||

|VCCQ_D11 | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|D12 | |||

|NU_D12 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|D13 | |||

|NU_D13 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|E1 | |||

|NU_E1 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|E2 | |||

|NU_E2 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|E3 | |||

|VSSQ_E3 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|E4 | |||

|DQ1[2] | |||

|S50_NAND_CH0_AD2 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|E5 | |||

|VSSQ_E5 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|E6 | |||

|DQS_1_T | |||

|D90_NAND_CH0_DQS_P | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|E8 | |||

|RE_1_T | |||

|D90_NAND_CH0_RE_P | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|E9 | |||

|VSSQ_E9 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|E10 | |||

|DQ1[5] | |||

|S50_NAND_CH0_AD5 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|E11 | |||

|VSSQ_E11 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|E12 | |||

|NU_E12 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|E13 | |||

|NU_E13 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|F3 | |||

|DQ1[0] | |||

|S50_NAND_CH0_AD0 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|F4 | |||

|DQ1[1] | |||

|S50_NAND_CH0_AD1 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|F5 | |||

|DQS_1_C | |||

|D90_NAND_CH0_DQS_N | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|F6 | |||

|RE_1_C | |||

|D90_NAND_CH0_RE_N | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|F8 | |||

|WE_1_N | |||

|S50_/NAND_CH0_CE0_WE | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|F9 | |||

|VREF_1 | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|F10 | |||

|DQ1[6] | |||

|S50_NAND_CH0_AD6 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|F11 | |||

|DQ1[7] | |||

|S50_NAND_CH0_AD7 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|G3 | |||

|VSSQ_G3 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|G4 | |||

|VCCQ_G4 | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|G5 | |||

|ALE_1 | |||

|S50_NAND_CH0_ALE | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|G6 | |||

|CLE_1 | |||

|S50_NAND_CH0_CLE | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|G8 | |||

|CE3_1_N | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|G9 | |||

|CE2_1_N | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|G10 | |||

|VCCQ_G10 | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|G11 | |||

|VSSQ_G11 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|H3 | |||

|NU_H3 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|H4 | |||

|NU_H4 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|H5 | |||

|WP_1_N | |||

|S50_/NAND_WP | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|H6 | |||

|NU_H6 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|H8 | |||

|CE1_1_N | |||

|S50_/NAND_CH0_CE1 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|H9 | |||

|CE0_1_N | |||

|S50_/NAND_CH0_CE0 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|H10 | |||

|RZQ_1 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|H11 | |||

|NU_H11 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|J3 | |||

|VSS_J3 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|J4 | |||

|VCC_J4 | |||

|2.5V_NAND_VCC | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|J5 | |||

|R/B0_0_N | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|J6 | |||

|R/B1_0_N | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|J8 | |||

|R/B1_1_N | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|J9 | |||

|R/B0_1_N | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|J10 | |||

|VCC_J10 | |||

|2.5V_NAND_VCC | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|J11 | |||

|VSS_J11 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|K3 | |||

|NU_K3 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|K4 | |||

|RZQ_0 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|K5 | |||

|CE0_0_N | |||

|S50_NAND_CH1_CE0 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|K6 | |||

|CE1_0_N | |||

|S50_NAND_CH1_CE1 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|K8 | |||

|VPP | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|K9 | |||

|WP_0_N | |||

|S50_/NAND_WP | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|K10 | |||

|NU_K10 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|K11 | |||

|NU_K11 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|L3 | |||

|VSSQ_L3 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|L4 | |||

|VCCQ_L4 | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|L5 | |||

|CE2_0_N | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|L6 | |||

|CE3_0_N | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|L8 | |||

|CLE_0 | |||

|S50_NAND_CH1_CLE | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|L9 | |||

|ALE_0 | |||

|S50_NAND_CH1_ALE | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|L10 | |||

|VCCQ_L10 | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|L11 | |||

|VSSQ_L11 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|M3 | |||

|DQ0[7] | |||

|S50_NAND_CH1_AD7 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|M4 | |||

|DQ0[6] | |||

|S50_NAND_CH1_AD6 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|M5 | |||

|VREF_0 | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|M6 | |||

|WE_0_N | |||

|S50_NAND_CH1_WE | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|M8 | |||

|RE_0_C | |||

|D90_NAND_CH1_RE_N | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|M9 | |||

|DQS_0_C | |||

|D50_NAND_CH1_DQS_N | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|M10 | |||

|DQ0[1] | |||

|S50_NAND_CH1_AD1 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|M11 | |||

|DQ0[0] | |||

|S50_NAND_CH1_AD0 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|N1 | |||

|NU_N1 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|N2 | |||

|NU_N2 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|N3 | |||

|VSSQ_N3 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|N4 | |||

|DQ0[5] | |||

|S50_NAND_CH1_AD5 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|N5 | |||

|VSSQ_N5 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|N6 | |||

|RE_0_T | |||

|D90_NAND_CH1_RE_P | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|N8 | |||

|DQS_0_T | |||

|D50_NAND_CH1_DQS_P | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|N9 | |||

|VSSQ_N9 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|N10 | |||

|DQ0[2] | |||

|S50_NAND_CH1_AD2 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|N11 | |||

|VSSQ_N11 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|N12 | |||

|NU_N12 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|N13 | |||

|NU_N13 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|P1 | |||

|NU_P1 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|P2 | |||

|NU_P2 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|P3 | |||

|VCCQ_P3 | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|P4 | |||

|VCCQ_P4 | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|P5 | |||

|DQ0[4] | |||

|S50_NAND_CH1_AD4 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|P6 | |||

|VCC_P6 | |||

|2.5V_NAND_VCC | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|P8 | |||

|VSS_P8 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|P9 | |||

|DQ0[3] | |||

|S50_NAND_CH1_AD3 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|P10 | |||

|VCCQ_P10 | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|P11 | |||

|VCCQ_P11 | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|P12 | |||

|NU_P12 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|P13 | |||

|NU_P13 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|R1 | |||

|NU_R1 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|R2 | |||

|NU_R2 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|R3 | |||

|NU_R3 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|R4 | |||

|NU_R4 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|R10 | |||

|NU_R10 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|R11 | |||

|NU_R11 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|R12 | |||

|NU_R12 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|R13 | |||

|NU_R13 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|T1 | |||

|NC_T1 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|T2 | |||

|NC_T2 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|T3 | |||

|NC_T3 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|T4 | |||

|NC_T4 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|T10 | |||

|NC_T10 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|T11 | |||

|NC_T11 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|T12 | |||

|NC_T12 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|T13 | |||

|NC_T13 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|U1 | |||

|NC_U1 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|U2 | |||

|NC_U2 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|U3 | |||

|NC_U3 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|U4 | |||

|NC_U4 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|U10 | |||

|NC_U10 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|U11 | |||

|NC_U11 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|U12 | |||

|NC_U12 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|U13 | |||

|NC_U13 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|} | |||

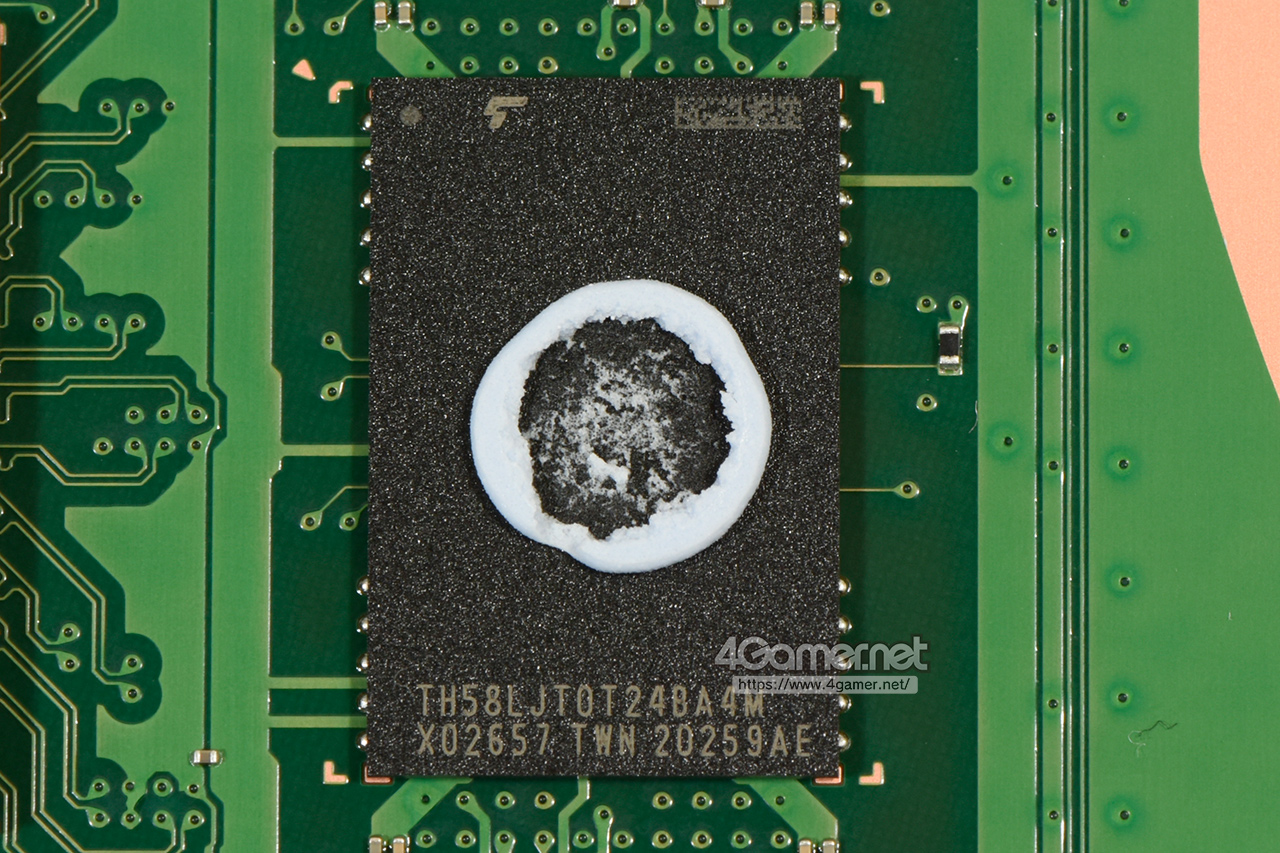

= Pictures = | = Pictures = | ||

| Line 15: | Line 940: | ||

* BLUE SSD RELATED | * BLUE SSD RELATED | ||

* ORANGE VCCQ | * ORANGE VCCQ | ||

* GREY VSSQ | |||

Latest revision as of 09:54, 14 December 2024

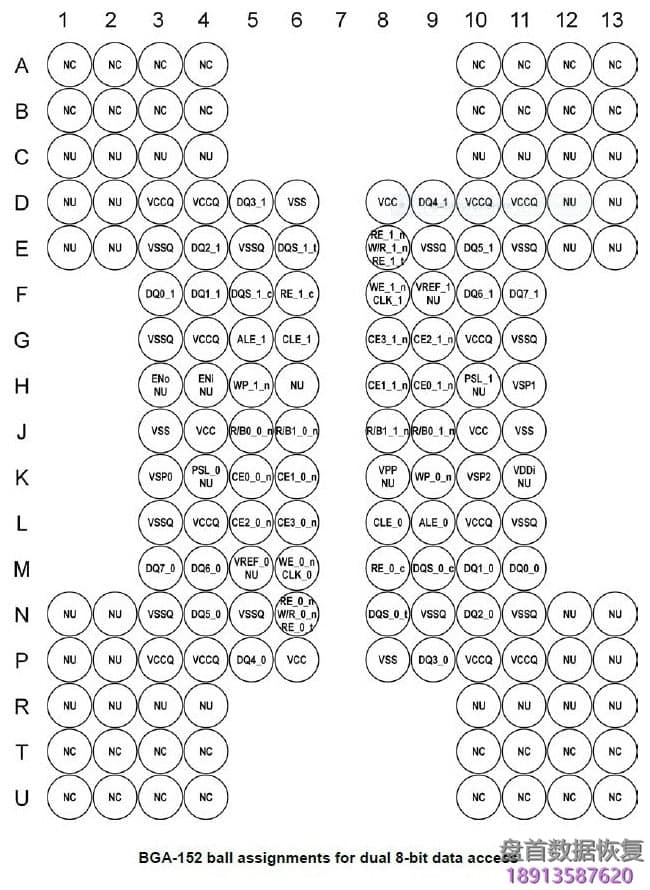

Pinout[edit | edit source]

There are six chips, each with identical inputs but assigned to different channels.

The first chip operates on channels 0 and 1, the second on channels 2 and 3, and so forth.

Pictures[edit | edit source]

Possible Pinout[edit | edit source]

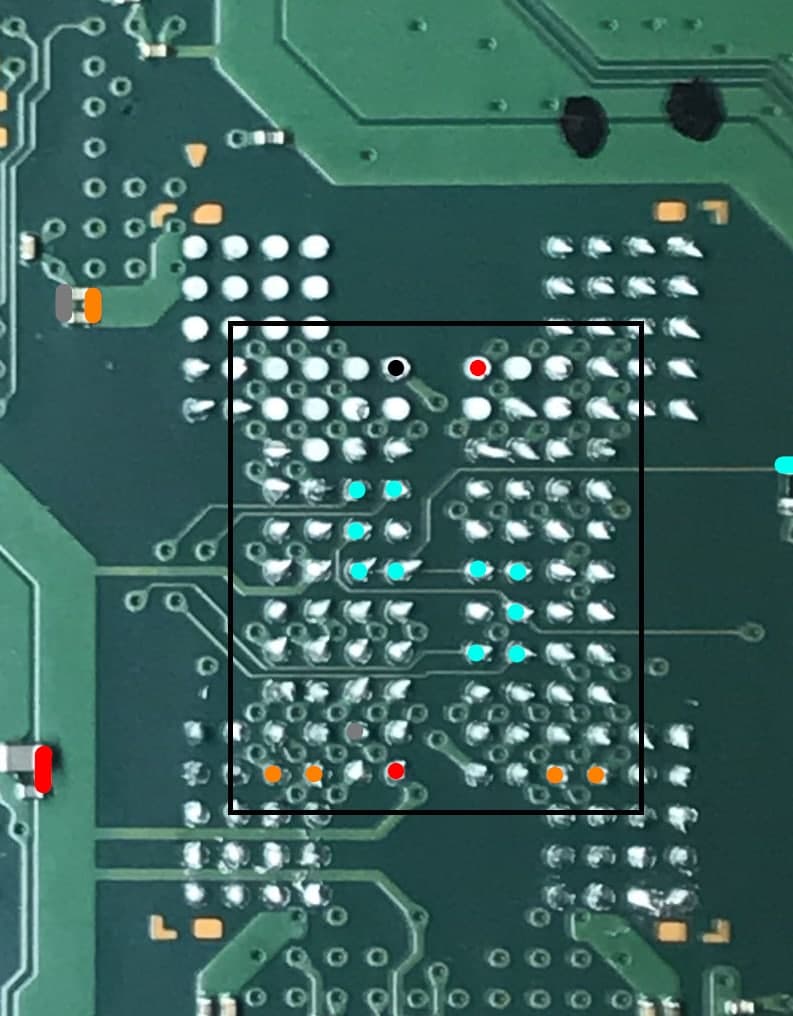

Tracing[edit | edit source]

- RED VCC

- BLACK VSS

- BLUE SSD RELATED

- ORANGE VCCQ

- GREY VSSQ