K4A4G085WF-BCTD: Difference between revisions

Jump to navigation

Jump to search

(→Pinout: Added description) |

|||

| (One intermediate revision by the same user not shown) | |||

| Line 1: | Line 1: | ||

= Pinout = | |||

{| class="wikitable mw-collapsible" | |||

|+ | |||

!Pad | |||

!Internal Name | |||

!External Name | |||

!Type | |||

!Description | |||

|- | |||

|A1 | |||

|VDD_A1 | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Power Supply: 1.2 V +/- 0.06 V | |||

|- | |||

|A2 | |||

|VSSQ_A2 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|DQ Ground | |||

|- | |||

|A3 | |||

|TDQS_c | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

|Termination Data Strobe | |||

|- | |||

|A7 | |||

|DM/DBI/TDQS_t | |||

|S50_FC_DDR_DM | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Input Data Mask and Data Bus Inversion | |||

|- | |||

|A8 | |||

|VSSQ_A8 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|DQ Ground | |||

|- | |||

|A9 | |||

|VSS_A9 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|B1 | |||

|BPP_B1 | |||

|2.5V_DDR4_VPP | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|DRAM Activation Power Supply: 2.5V (2.375V min , 2.75 max) | |||

|- | |||

|B2 | |||

|VDDQ_B2 | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|DQ Power Supply: 1.2 V +/- 0.06 V | |||

|- | |||

|B3 | |||

|DQS_c | |||

|D90_FC_DDR_DQS0_N | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

|Data Strobe | |||

|- | |||

|B7 | |||

|DQ1 | |||

|S50_FC_DDR_D0 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

|Data Input/ Output | |||

|- | |||

|B8 | |||

|VDDQ_B8 | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|DQ Power Supply: 1.2 V +/- 0.06 V | |||

|- | |||

|B9 | |||

|ZQ | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Reference Pin for ZQ calibration | |||

|- | |||

|C1 | |||

|VDDQ_C1 | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|DQ Power Supply: 1.2 V +/- 0.06 V | |||

|- | |||

|C2 | |||

|DQ0 | |||

|S50_FC_DDR_D3 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

|Data Input/ Output | |||

|- | |||

|C3 | |||

|DQS_t | |||

|D90_FC_DDR_DQS0_P | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

|Data Strobe | |||

|- | |||

|C7 | |||

|VDD_C7 | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Power Supply: 1.2 V +/- 0.06 V | |||

|- | |||

|C8 | |||

|VSS_C8 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|C9 | |||

|VDDQ_C9 | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|DQ Power Supply: 1.2 V +/- 0.06 V | |||

|- | |||

|D1 | |||

|VSSQ_D1 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|DQ Ground | |||

|- | |||

|D2 | |||

|DQ4 | |||

|S50_FC_DDR_D4 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

|Data Input/ Output | |||

|- | |||

|D3 | |||

|DQ2 | |||

|S50_FC_DDR_D5 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

|Data Input/ Output | |||

|- | |||

|D7 | |||

|DQ3 | |||

|S50_FC_DDR_D2 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

|Data Input/ Output | |||

|- | |||

|D8 | |||

|DQ5 | |||

|S50_FC_DDR_D1 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

|Data Input/ Output | |||

|- | |||

|D9 | |||

|VSSQ_D9 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|DQ Ground | |||

|- | |||

|E1 | |||

|VSS_E1 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|E2 | |||

|VDDQ_E2 | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|DQ Power Supply: 1.2 V +/- 0.06 V | |||

|- | |||

|E3 | |||

|DQ6 | |||

|S50_FC_DDR_D6 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

|Data Input/ Output | |||

|- | |||

|E7 | |||

|DQ7 | |||

|S50_FC_DDR_D7 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

|Data Input/ Output | |||

|- | |||

|E8 | |||

|VDDQ_E8 | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|DQ Power Supply: 1.2 V +/- 0.06 V | |||

|- | |||

|E9 | |||

|VSS_E9 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|F1 | |||

|VDD_F1 | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Power Supply: 1.2 V +/- 0.06 V | |||

|- | |||

|F2 | |||

|NC_F2 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

|No Connect | |||

|- | |||

|F3 | |||

|ODT | |||

|S50_FC_DDR_ODT0 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|On Die Termination | |||

|- | |||

|F7 | |||

|CK_t | |||

|D90_FC_DDR_CLOCK0_P | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Clock | |||

|- | |||

|F8 | |||

|CK_c | |||

|D90_FC_DDR_CLOCK0_N | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Clock | |||

|- | |||

|F9 | |||

|VDD_F9 | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Power Supply: 1.2 V +/- 0.06 V | |||

|- | |||

|G1 | |||

|VSS_G1 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|G2 | |||

|NC_G2 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

|No Connect | |||

|- | |||

|G3 | |||

|CKE | |||

|S50_FC_DDR_CKE0 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Clock Enable | |||

|- | |||

|G7 | |||

|\CS | |||

|S50_FC_DDR_CS0N | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Chip Select | |||

|- | |||

|G8 | |||

|NC_G8 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

|No Connect | |||

|- | |||

|G9 | |||

|NC_G9 | |||

|TEN | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Connectivity Test Mode Enable | |||

|- | |||

|H1 | |||

|VDD_H1 | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Power Supply: 1.2 V +/- 0.06 V | |||

|- | |||

|H2 | |||

|\WE/A14 | |||

|S50_FC_DDR_WEN | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Command Inputs | |||

|- | |||

|H3 | |||

|\ACT | |||

|S50_FC_DDR_A14 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Activision Command Input | |||

|- | |||

|H7 | |||

|\CAS | |||

|S50_/FC_DDR_CASN | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Command Inputs | |||

|- | |||

|H8 | |||

|\RAS | |||

|S50_/FC_DDR_RASN | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Command Inputs | |||

|- | |||

|H9 | |||

|VSS_G9 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|J1 | |||

|VREFCA | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Reference voltage for CA | |||

|- | |||

|J2 | |||

|BG0 | |||

|S50_FC_DDR_BA2 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Bank Group Inputs | |||

|- | |||

|J3 | |||

|A10/AP | |||

|S50_FC_DDR_A10 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Auto-precharge | |||

|- | |||

|J7 | |||

|A12/\BC | |||

|S50_FC_DDR_A12 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Burst Chop | |||

|- | |||

|J8 | |||

|BG1 | |||

|S50_FC_DDR_A15 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Bank Group Inputs | |||

|- | |||

|J9 | |||

|VDD_J9 | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Power Supply: 1.2 V +/- 0.06 V | |||

|- | |||

|K1 | |||

|VSS_K1 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|K2 | |||

|BA0 | |||

|S50_FC_DDR_BA0 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Bank Address Inputs | |||

|- | |||

|K3 | |||

|A4 | |||

|S50_FC_DDR_A4 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Address Inputs | |||

|- | |||

|K7 | |||

|A3 | |||

|S50_FC_DDR_A3 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Address Inputs | |||

|- | |||

|K8 | |||

|BA1 | |||

|S50_FC_DDR_BA1 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Bank Address Inputs | |||

|- | |||

|K9 | |||

|VSS_K9 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|L1 | |||

|\RESET | |||

|S50_/FC_DDR_RSTN | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Active Low Asynchronous Reset | |||

|- | |||

|L2 | |||

|A6 | |||

|S50_FC_DDR_A6 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Address Inputs | |||

|- | |||

|L3 | |||

|A0 | |||

|S50_FC_DDR_A0 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Address Inputs | |||

|- | |||

|L7 | |||

|A1 | |||

|S50_FC_DDR_A1 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Address Inputs | |||

|- | |||

|L8 | |||

|A5 | |||

|S50_FC_DDR_A5 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Address Inputs | |||

|- | |||

|L9 | |||

|\ALERT | |||

|S50_/FC_DDR_ALERTN | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Alert | |||

|- | |||

|M1 | |||

|VDD_M1 | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Power Supply: 1.2 V +/- 0.06 V | |||

|- | |||

|M2 | |||

|A8 | |||

|S50_FC_DDR_A8 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Address Inputs | |||

|- | |||

|M3 | |||

|A2 | |||

|S50_FC_DDR_A2 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Address Inputs | |||

|- | |||

|M7 | |||

|A9 | |||

|S50_FC_DDR_A9 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Address Inputs | |||

|- | |||

|M8 | |||

|A7 | |||

|S50_FC_DDR_A7 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Address Inputs | |||

|- | |||

|M9 | |||

|VPP_M9 | |||

|2.5V_DDR4_VPP | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|DRAM Activation Power Supply: 2.5V (2.375V min , 2.75 max) | |||

|- | |||

|N1 | |||

|VSS_N1 | |||

|GND | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Ground | |||

|- | |||

|N2 | |||

|A11 | |||

|S50_FC_DDR_A11 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Address Inputs | |||

|- | |||

|N3 | |||

|PAR | |||

|S50_FC_DDR_PAR | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Command and Address Parity Input | |||

|- | |||

|N7 | |||

|NC_N7 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

|No Connect | |||

|- | |||

|N8 | |||

|A13 | |||

|S50_FC_DDR_A13 | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Address Inputs | |||

|- | |||

|N9 | |||

|VDD_N9 | |||

|1.2V_FC_VDDQMIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

|Power Supply: 1.2 V +/- 0.06 V | |||

|- | |||

|} | |||

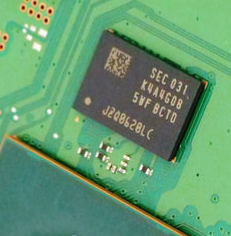

= Pictures = | = Pictures = | ||

[[File:K4A4G085WF-BCTD.png]] | [[File:K4A4G085WF-BCTD.png]] | ||

[[File:K4A4G085WF-BCTD_Proto.png]] | [[File:K4A4G085WF-BCTD_Proto.png]] | ||