CXD90062GG: Difference between revisions

Jump to navigation

Jump to search

(→Pinout: Added CH0,1) |

|||

| Line 1,060: | Line 1,060: | ||

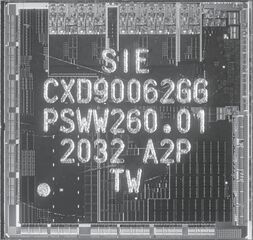

= Pictures = | = Pictures = | ||

[[File:CXD90062GG.jpeg]]<br> | [[File:CXD90062GG.jpeg|253x253px]]<br> | ||

[[File:CXD90062GG2.jpeg]]<br> | [[File:CXD90062GG2.jpeg|253x253px]]<br> | ||

[[File:50980106477 3117f2d5c0 o.jpg| | [[File:50980106477 3117f2d5c0 o.jpg|253x253px]] | ||

[[File:CXD90062GG_Proto.png]] | [[File:CXD90062GG_Proto.png|253x253px]] | ||

== Sources == | == Sources == | ||

https://www.flickr.com/photos/130561288@N04/albums/72157718290760702 | https://www.flickr.com/photos/130561288@N04/albums/72157718290760702 | ||

Revision as of 23:49, 12 December 2024

NVME Controller

Pinout

Pictures

Sources

https://www.flickr.com/photos/130561288@N04/albums/72157718290760702