CXD90062GG: Difference between revisions

Jump to navigation

Jump to search

(→Pinout: Added GPIO&TEST and UART, also reorganize alphabetically.) |

(→Pinout: Added CH0,1) |

||

| Line 11: | Line 11: | ||

!Type | !Type | ||

!Description | !Description | ||

|- | |||

|AA1 | |||

|PIN_AD_CH1[1] | |||

|S50_NAND_CH1_AD1 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|AA2 | |||

|PIN_AD_CH1[0] | |||

|S50_NAND_CH1_AD0 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|AA4 | |||

|PIN_CLE_CH0 | |||

|S50_NAND_CH0_CLE | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AA5 | |||

|PIN_CE2_CH0 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|AA6 | |||

|PIN_CE3_CH0 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |- | ||

|AA12 | |AA12 | ||

| Line 70: | Line 100: | ||

|D100G_FC_PCIE_CLK_N | |D100G_FC_PCIE_CLK_N | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |||

|- | |||

|AB1 | |||

|PIN_CE1_CH0 | |||

|S50_/NAND_CH2_CE1 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AB2 | |||

|PIN_CE0_CH0 | |||

|S50_/NAND_CH2_CE0 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AB3 | |||

|PIN_ALE_CH0 | |||

|S50_NAND_CH0_ALE | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AB4 | |||

|PIN_AD_CH0[5] | |||

|S50_NAND_CH0_AD5 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|AB5 | |||

|PIN_AD_CH0[3] | |||

|S50_NAND_CH0_AD3 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | | | ||

|- | |- | ||

| Line 166: | Line 226: | ||

| | | | ||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |[[File:Pin-nc.png|alt=Not connected|frameless]] | ||

| | |||

|- | |||

|AC1 | |||

|PIN_REB_CH0 | |||

|D90_NAND_CH0_RE_ N S50_/ | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AC2 | |||

|PIN_RE_CH0 | |||

|D90_NAND_CH0_RE_P | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AC4 | |||

|PIN_AD_CH0[4] | |||

|S50_NAND_CH0_AD4 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|AC5 | |||

|PIN_AD_CH0[2] | |||

|S50_NAND_CH0_AD2 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | | | ||

|- | |- | ||

| Line 244: | Line 328: | ||

|S50G_FC_SYSCLK | |S50G_FC_SYSCLK | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |||

|- | |||

|AD2 | |||

|PIN_WE_CH0 | |||

|S50_NANO_CH0_WE | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|AD3 | |||

|PIN_AD_CH0[7] | |||

|S50_NAND_CH0_AD7 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|AD4 | |||

|PIN_DQSB_CH0 | |||

|D90_NAND_CH0_DQS_N | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|AD5 | |||

|PIN_AD_CH0[0] | |||

|S50_NAND_CH0_AD0 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | | | ||

|- | |- | ||

| Line 346: | Line 454: | ||

| | | | ||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |[[File:Pin-nc.png|alt=Not connected|frameless]] | ||

| | |||

|- | |||

|AE3 | |||

|PIN_AD_CH0[6] | |||

|S50_NAND_CH0_AD6 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|AE4 | |||

|PIN_DQS_CH0 | |||

|D90_NAND_CH0_DQS_P | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|AE5 | |||

|PIN_AD_CH0[1] | |||

|S50_NAND_CH0_AD1 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | | | ||

|- | |- | ||

| Line 501: | Line 627: | ||

|PIN_RXP_RC1_2 | |PIN_RXP_RC1_2 | ||

|D85_M2_PCIE_RX2P | |D85_M2_PCIE_RX2P | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | |||

|- | |||

|H13 | |||

|PIN_VREF_NF[1] | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | | | ||

| Line 550: | Line 682: | ||

|D85_SOC_PCIE_TX3N | |D85_SOC_PCIE_TX3N | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |||

|- | |||

|M8 | |||

|PIN_CAL_NF | |||

|S50_/NAND_WP | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | | | ||

|- | |- | ||

| Line 562: | Line 700: | ||

|D85_SOC_PCIE_RX3N | |D85_SOC_PCIE_RX3N | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | |||

|- | |||

|N8 | |||

|PIN_VREF_NF[0] | |||

|1.2V_FC_VDDQFIO | |||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |||

| | | | ||

|- | |- | ||

| Line 640: | Line 784: | ||

|D85_SOC_PCIE_TX0N | |D85_SOC_PCIE_TX0N | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |||

|- | |||

|V1 | |||

|PIN_RE_CH1 | |||

|D90_NAND_CH1_RE_ P | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|V2 | |||

|PIN_REB_CH1 | |||

|D90_NAND_CH1_RE_ N S50_/ | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|V3 | |||

|PIN_CE1_CH1 | |||

|S50_/NAND_CH2_CE1 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|V4 | |||

|PIN_CE0_CH1 | |||

|S50_/NAND_CH2_CE0 | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|V5 | |||

|PIN_ALE_CH1 | |||

|S50_NAND_CH1_ALE | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|V6 | |||

|PIN_CLE_CH1 | |||

|S50_NAND_CH1_CLE | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | | | ||

|- | |- | ||

| Line 688: | Line 868: | ||

|D85_SOC_PCIE_RX0N | |D85_SOC_PCIE_RX0N | ||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |[[File:Pin out.png|alt=Output|frameless|24x24px]] | ||

| | |||

|- | |||

|W1 | |||

|PIN_AD_CH1[7] | |||

|S50_NAND_CH1_AD7 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|W2 | |||

|PIN_AD_CH1[6] | |||

|S50_NAND_CH1_AD6 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|W4 | |||

|PIN_AD_CH1[5] | |||

|S50_NAND_CH1_AD5 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|W5 | |||

|PIN_WE_CH1 | |||

|NAND_CH1_WE | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | |||

|- | |||

|W6 | |||

|PIN_CE2_CH1 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | |||

|- | |||

|W7 | |||

|PIN_CE3_CH1 | |||

| | |||

|[[File:Pin-nc.png|alt=Not connected|frameless]] | |||

| | | | ||

|- | |- | ||

| Line 748: | Line 964: | ||

|D85_FC_RX0P | |D85_FC_RX0P | ||

|[[File:IC-Pin-in.png|alt=Input|frameless]] | |[[File:IC-Pin-in.png|alt=Input|frameless]] | ||

| | |||

|- | |||

|Y1 | |||

|PIN_DQSB_CH1 | |||

|D90_NAND_CH1_DQS_ P | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|Y2 | |||

|PIN_DQS_CH1 | |||

|D90_NAND_CH1_DQS_ N | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|Y3 | |||

|PIN_AD_CH1[4] | |||

|S50_NAND_CH1_AD4 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|Y4 | |||

|PIN_AD_CH1[3] | |||

|S50_NAND_CH1_AD3 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|Y5 | |||

|PIN_AD_CH1[2] | |||

|S50_NAND_CH1_AD2 | |||

|[[File:IC-Pin-Out.png|alt=Others|frameless]] | |||

| | |||

|- | |||

|Y7 | |||

|PIN_WP | |||

|S50_/NAND_WP | |||

|[[File:Pin out.png|alt=Output|frameless|24x24px]] | |||

| | | | ||

|- | |- | ||

Revision as of 20:57, 12 December 2024

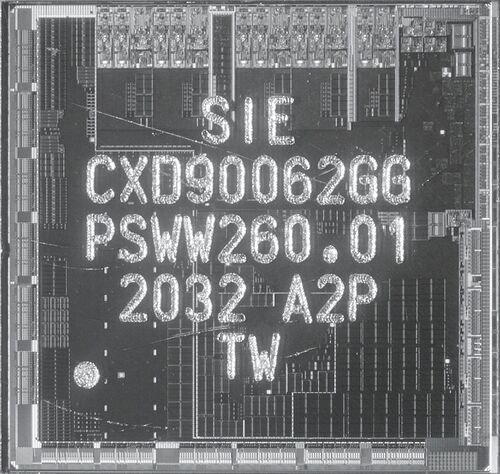

NVME Controller

Pinout

Pictures

Sources

https://www.flickr.com/photos/130561288@N04/albums/72157718290760702