Service Connectors: Difference between revisions

Jump to navigation

Jump to search

CelesteBlue (talk | contribs) No edit summary |

|||

| (39 intermediate revisions by 3 users not shown) | |||

| Line 5: | Line 5: | ||

== First Connector (5 Pins) == | == First Connector (5 Pins) == | ||

< | [[File:I2NazzQ.png]] | ||

[[File:5_Pin_Service_Layout_Proto.jpg]] | |||

== Second Connector (24 Pins) == | |||

[[File:qdw8Nxb.png]] | |||

[[File:24_Pin_Service_Connector_Proto.png]] | |||

[[File:Screenshot 2023-11-24 at 9.38.03 PM.png]] | |||

== Third Connector (24 Pins) (Bluray) == | |||

[[File:24_Pin_Bluray_Service_Connector_Proto.png]] | |||

= Meaning of Pins = | |||

* Starts at Leftmost (Indicated by Arrow) | |||

== 5 Pins == | |||

{| class="wikitable sortable" | |||

|- | |||

! PIN # (24 PIN#) !! Meaning !! Notes | |||

|- | |||

| 1 || GND || Ground Plane | |||

|- | |||

| 2(7) || SSB_UART0_TX || SouthBridge UART0 Transmit. Used to send commands to EMC. command always <com>:<chk>\r\n | |||

|- | |||

| 3(6) || SSB_UART0_RX || SouthBridge UART0 Receive. Used to receive responses from EMC. response always <res>:<chk>\r\n | |||

|- | |||

| 4(14) || FC_UART2_TX || Flash Controller UART2 Transmit. (bootrom: 460800, eap fw, apu: 230400) | |||

|- | |||

| 5(13) || FC_UART2_RX || Flash Controller UART2 Receive. (bootrom: 460800, eap fw, apu: 230400) | |||

|- | |||

|} | |||

== 24 Pins == | |||

* Major credits to shuffle2 for the complete pinout. | |||

{| class="wikitable sortable" | |||

! PIN # !! Meaning !! Notes | |||

|- | |||

| 1 || VDD || 5v | |||

|- | |||

| 2 || VDD || 5v | |||

|- | |||

| 3 || GND || Ground Plane | |||

|- | |||

| 4 || GND || Ground Plane | |||

|- | |||

| 5 || SSB_BOOT_STRAP_1 || SouthBridge Boot Strap 1. pulling low at emc boot causes emc rom to enter uart shell @ 460800 | |||

|- | |||

| 6 || SSB_UART0_RX || SouthBridge UART0 Receive. Used to receive responses from EMC. response always <res>:<chk>\r\n (uart rx emc 115200) | |||

|- | |||

| 7 || SSB_UART0_TX || SouthBridge UART0 Transmit. Used to send commands to EMC. command always <com>:<chk>\r\n (uart tx emc 115200) | |||

|- | |||

| 8 || 3v3 || goes low when [[EMC]] resets | |||

|- | |||

| 9 || 0v || 0v | |||

|- | |||

| 10 || GND || Ground Plane | |||

|- | |||

| 11 || FC_UART1_TX || Flash Controller UART1 Transmit. (efc fw: 460800) | |||

|- | |||

| 12 || FC_UART1_RX || Flash Controller UART1 Receive. (efc fw: 460800) | |||

|- | |||

| 13 || FC_UART2_RX || Flash Controller UART2 Receive. (bootrom: 460800, eap fw, apu: 230400) | |||

|- | |||

| 14 || FC_UART2_TX || Flash Controller UART2 Transmit. (bootrom: 460800, eap fw, apu: 230400) | |||

|- | |||

| 15 || GND || Ground Plane | |||

|- | |||

| 16 || emc gpio c5 || ("GPI SW" (only used if devif_det# active)) | |||

|- | |||

| 17 || 0v || 0v | |||

|- | |||

| 18 || 5v || 5v | |||

|- | |||

| 19 || emc gpio a49 || [[EMC]] GPIO a49 | |||

|- | |||

| 20 || emc gpio a27 || [[EMC]] GPIO a27. main power switch | |||

|- | |||

| 21 || i2c data || i2c data (i2c_bus_4) | |||

|- | |||

| 22 || i2c clock || i2c clock (i2c_bus_4) | |||

|- | |||

| 23 || GND || Ground Plane | |||

|- | |||

| 24 || /SSB_RESET || SouthBridge Reset. emc reset# | |||

|} | |||

Latest revision as of 11:27, 9 December 2024

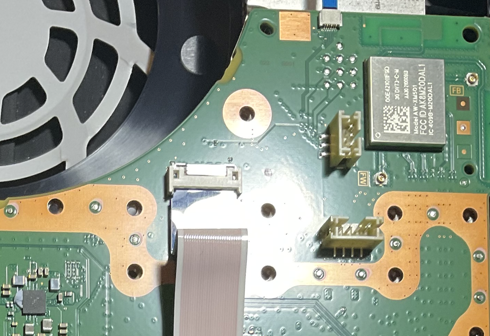

There are two Service Connectors on the PS5:

Pictures[edit | edit source]

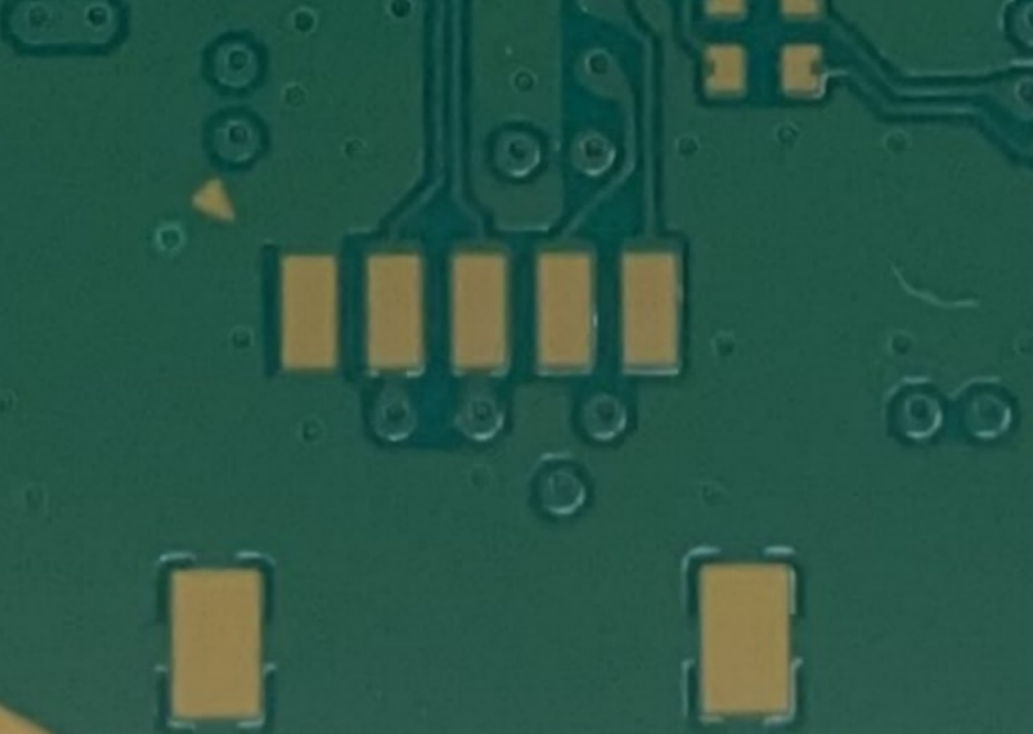

First Connector (5 Pins)[edit | edit source]

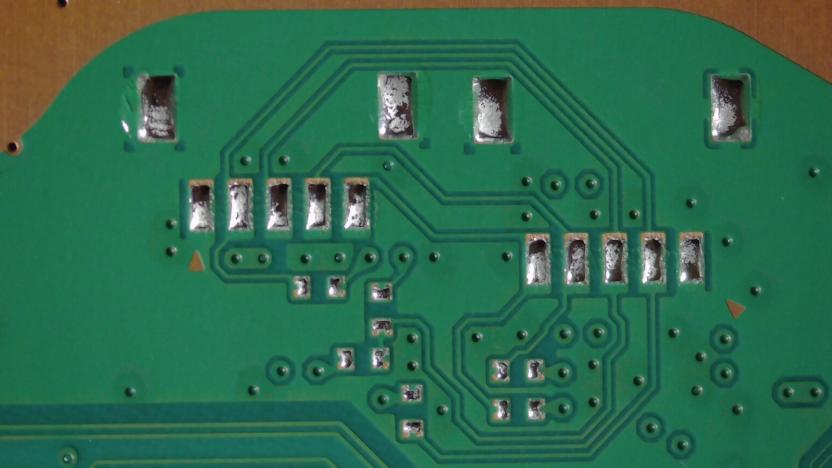

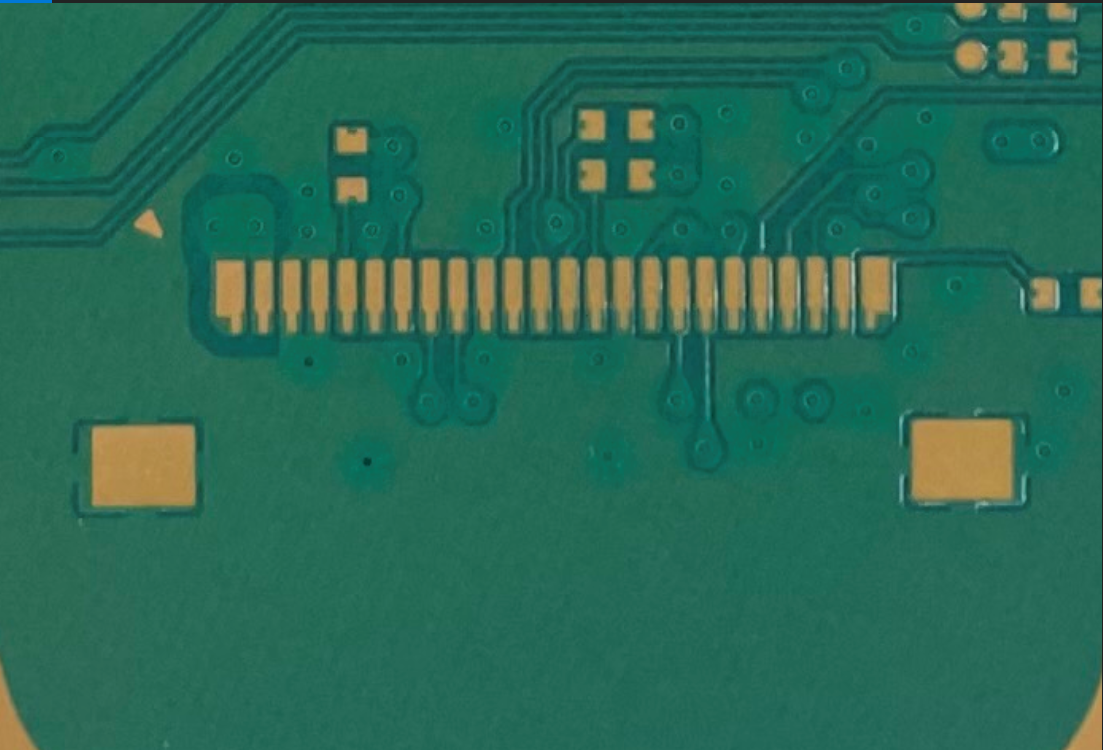

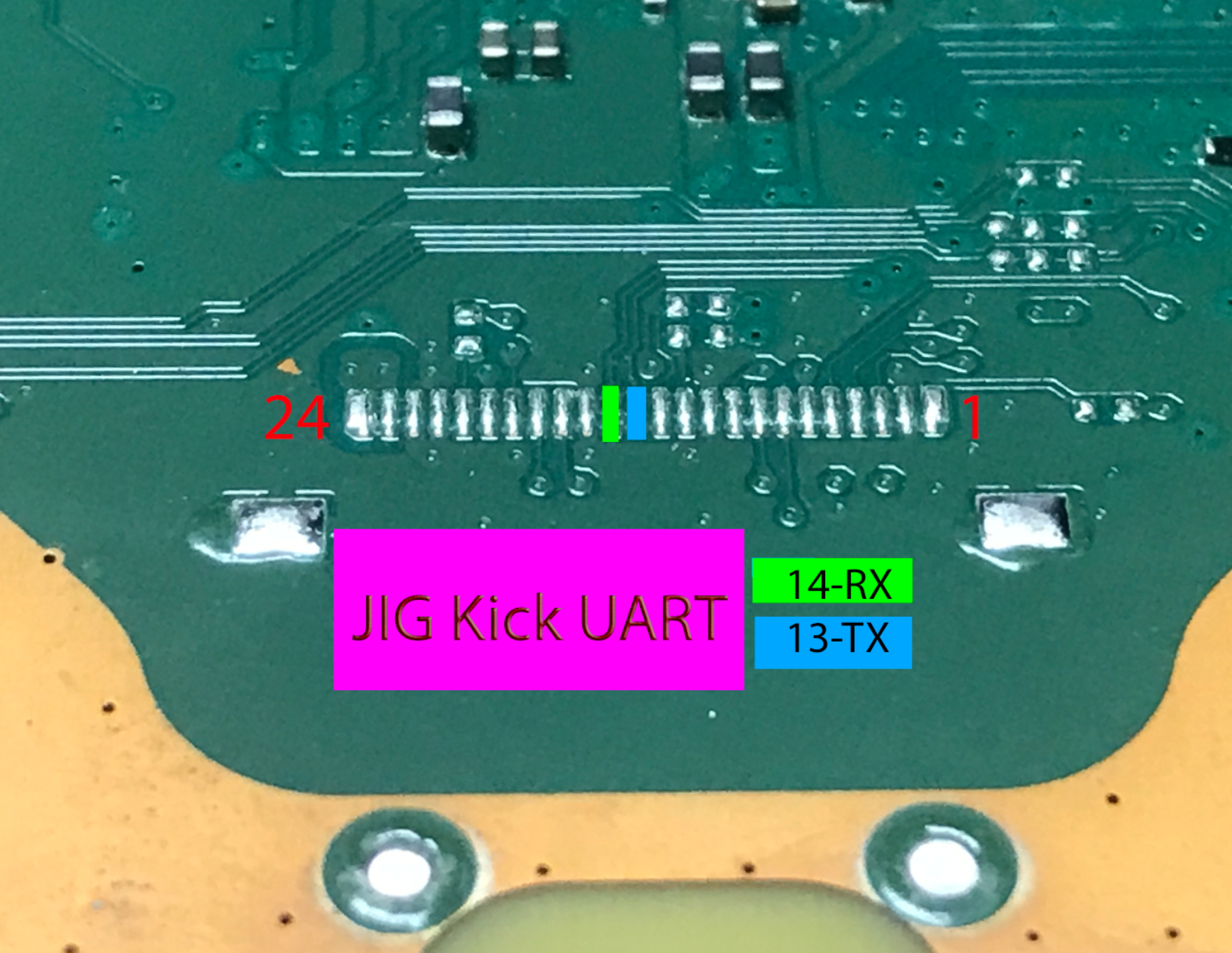

Second Connector (24 Pins)[edit | edit source]

Third Connector (24 Pins) (Bluray)[edit | edit source]

Meaning of Pins[edit | edit source]

- Starts at Leftmost (Indicated by Arrow)

5 Pins[edit | edit source]

| PIN # (24 PIN#) | Meaning | Notes |

|---|---|---|

| 1 | GND | Ground Plane |

| 2(7) | SSB_UART0_TX | SouthBridge UART0 Transmit. Used to send commands to EMC. command always <com>:<chk>\r\n |

| 3(6) | SSB_UART0_RX | SouthBridge UART0 Receive. Used to receive responses from EMC. response always <res>:<chk>\r\n |

| 4(14) | FC_UART2_TX | Flash Controller UART2 Transmit. (bootrom: 460800, eap fw, apu: 230400) |

| 5(13) | FC_UART2_RX | Flash Controller UART2 Receive. (bootrom: 460800, eap fw, apu: 230400) |

24 Pins[edit | edit source]

- Major credits to shuffle2 for the complete pinout.

| PIN # | Meaning | Notes |

|---|---|---|

| 1 | VDD | 5v |

| 2 | VDD | 5v |

| 3 | GND | Ground Plane |

| 4 | GND | Ground Plane |

| 5 | SSB_BOOT_STRAP_1 | SouthBridge Boot Strap 1. pulling low at emc boot causes emc rom to enter uart shell @ 460800 |

| 6 | SSB_UART0_RX | SouthBridge UART0 Receive. Used to receive responses from EMC. response always <res>:<chk>\r\n (uart rx emc 115200) |

| 7 | SSB_UART0_TX | SouthBridge UART0 Transmit. Used to send commands to EMC. command always <com>:<chk>\r\n (uart tx emc 115200) |

| 8 | 3v3 | goes low when EMC resets |

| 9 | 0v | 0v |

| 10 | GND | Ground Plane |

| 11 | FC_UART1_TX | Flash Controller UART1 Transmit. (efc fw: 460800) |

| 12 | FC_UART1_RX | Flash Controller UART1 Receive. (efc fw: 460800) |

| 13 | FC_UART2_RX | Flash Controller UART2 Receive. (bootrom: 460800, eap fw, apu: 230400) |

| 14 | FC_UART2_TX | Flash Controller UART2 Transmit. (bootrom: 460800, eap fw, apu: 230400) |

| 15 | GND | Ground Plane |

| 16 | emc gpio c5 | ("GPI SW" (only used if devif_det# active)) |

| 17 | 0v | 0v |

| 18 | 5v | 5v |

| 19 | emc gpio a49 | EMC GPIO a49 |

| 20 | emc gpio a27 | EMC GPIO a27. main power switch |

| 21 | i2c data | i2c data (i2c_bus_4) |

| 22 | i2c clock | i2c clock (i2c_bus_4) |

| 23 | GND | Ground Plane |

| 24 | /SSB_RESET | SouthBridge Reset. emc reset# |