Template:Syscon pinout BGA 200 pads: Difference between revisions

Jump to navigation

Jump to search

No edit summary |

No edit summary |

||

| (43 intermediate revisions by the same user not shown) | |||

| Line 6: | Line 6: | ||

<div style="overflow:auto; <includeonly>height:800px;</includeonly>"> | <div style="overflow:auto; <includeonly>height:800px;</includeonly>"> | ||

{|class="wikitable sortable" style="width:100%; line-height: | {|class="wikitable sortable" style="width:100%; line-height:1em; font-size:0.9em" | ||

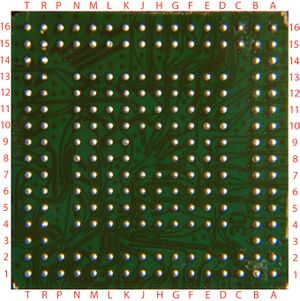

|+ {{captionlinks|Syscon pinout BGA 200 pads}} | |+ {{captionlinks|Syscon pinout BGA 200 pads}} | ||

|- | |- | ||

! Pad | ! Pad !! Port !! Name !! Type !! Description | ||

|- | |- | ||

| | | data-sort-value="A01" | A1 || data-sort-value="ZNC" | || data-sort-value="ZNC" | || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected | ||

|- | |- | ||

| | | data-sort-value="A02" | A2 || J || DISC_IN || ? || Connected to BluRay Drive connector (CN3221) pin 52 | ||

|- | |- | ||

| | | data-sort-value="A03" | A3 || J || SW_0 || ? || Connected to [[Regulators#Fujitsu_MB39A116PFT_.282_channel_DC.2FDC_converter.29 | Fujitsu MB39A116PFT]] (IC6003) pin 9 (switches +5V_MISC)<br>Connected to [[Regulators#Fujitsu_MB39A116PFT_.282_channel_DC.2FDC_converter.29 | Fujitsu MB39A116PFT]] (IC6003) pin 10 (switches +3.3V_MISC)<br>Connected to [[Components#Texas_Instruments_SN105233DBTR|Texas Instruments SN105233DBTR]] (IC6301) pin 10 (switches +1.7_MISC) | ||

|- | |- | ||

| | | data-sort-value="A04" | A4 || J || SW_8_C || ? || Connected to [[Components#Texas_Instruments_SN105233DBTR|Texas Instruments SN105233DBTR]] (IC6301) pin 9 (switches +1.8V_RSX_FBVDDQ)<br>Connected to [[Regulators#OnSemi_NCP511SN18T1_.281.8V_150_mA_CMOS_Low_Iq_Low-Dropout_Voltage_Regulator.29 | OnSemi NCP511SN18T1]] (IC6008) pin 3 (switches +1.8V_RSX_PLL_VDD) | ||

|- | |- | ||

| | | data-sort-value="A05" | A5 || J || DISC_OUT12_SW || ? || Connected to BluRay Drive connector (CN3221) pin 58 | ||

|- | |- | ||

| | | data-sort-value="A06" | A6 || R || MC_RESERVED2 || ? || Not connected to BluRay Drive because a missing resistor (R4080). BD_LED | ||

|- | |- | ||

| | | data-sort-value="A07" | A7 || R || MC_ALIVE || ? || Connected to BluRay Drive connector (CN3221) pin 47 | ||

|- | |- | ||

| | | data-sort-value="A08" | A8 || K || SB_SPI_CLK || ? || Southbridge SPI Bus | ||

|- | |- | ||

| | | data-sort-value="A09" | A9 || K || SB_SPI_DI || ? || Southbridge SPI Bus | ||

|- | |- | ||

| | | data-sort-value="A10" | A10 || K || DVE_I2C_SCL || ? || Connected to Digital Video Encoder [[CXM4024R]] pin 35 | ||

|- | |- | ||

| | | data-sort-value="A11" | A11 || K || ACDC_STBY || ? || Connected to [[Power Supply]] (small connector). This signal enables +12V_MAIN power rail (big prongs) | ||

|- | |- | ||

| | | data-sort-value="A12" | A12 || E || EJECT_SW || ? || Connected to [[Switch_boards|Switch board]] [[CSW-001]] connector pin 5 | ||

|- | |- | ||

| | | data-sort-value="A13" | A13 || E || SB_EBUS_RESET || ? || SS2_RESET (StarShip2 related), not connected because a missing resistor (R4135) ? | ||

|- | |- | ||

| | | data-sort-value="A14" | A14 || E || PE3 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected (CL4094) | ||

|- | |- | ||

| | | data-sort-value="A15" | A15 || E || BE_POW_FAIL || ? || Connected to [[Regulators#OnSemi_NCP5318FTR2G_.28Two.2FThree.2FFour-Phase_Buck_CPU_Controller.29|OnSemi NCP5318FTR2G]] (IC6103) pin 7 | ||

|- | |- | ||

| | | data-sort-value="A16" | A16 || data-sort-value="ZNC" | || data-sort-value="ZNC" | || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected | ||

|- | |- | ||

| | | data-sort-value="A99" style="padding:0px" | || colspan="4" data-sort-value="ZZZ" style="padding:0px" | | ||

|- | |- | ||

| | | data-sort-value="B01" | B1 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#c33|#fff}} AVREF1 || {{pini}} || data-sort-value="ZV33" style="color:#888" | +3.3V_EVER | ||

|- | |- | ||

| | | data-sort-value="B02" | B2 || J || DISC_OUT8_SW || ? || Connected to BluRay Drive connector (CN3221) pin 57 | ||

|- | |- | ||

| | | data-sort-value="B03" | B3 || J || PJ3 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected (CL4089) | ||

|- | |- | ||

| | | data-sort-value="B04" | B4 || J || SW_8_B || ? || Connected to [[Regulators#Mitsumi_MM1561JFBE_.28Low-Saturation_500mA_Regulators.29|Mitsumi MM1561JFBE]] (IC2408) pin 5 (switches +1.8V_ANA)<br>Connected to [[Regulators#Mitsumi_MM1593DFBEG_.28Low-Saturation_300mA_Regulators.29|Mitsumi MM1593DFBEG]] (IC2407) pin 5 (switches +3.3V_ANA)<br>Connected to transistor DTC144EUA-T106 (Q2401) base pin (switches +5V_ANA ?)<br>Connected to [[Regulators#OnSemi_NCP511SN15T1G_.281.5_V_150_mA_CMOS_Low_Iq_Low_Dropout_Voltage_Regulator_-_TSOP-5.29|OnSemi NCP511SN15T1G]] (IC6019) pin 3 (switches +1.5V_AVCG_VDDIO)<br>Connected to [[Regulators#Rohm_BD3521FVM-TR_.28Single_channel_Regulator_Driver_IC.29|Rohm BD3521FVM-TR]] (IC6017) pin 3 (switches +1.5V_RSX_VDDIO) | ||

|- | |- | ||

| | | data-sort-value="B05" | B5 || J || DVE_RST || ? || Connected to Digital Video Encoder [[CXM4024R]] pin 31 ? | ||

|- | |- | ||

| | | data-sort-value="B06" | B6 || R || MC_P_OFF_REQ || ? || Connected to BluRay Drive connector (CN3221) pin 48 | ||

|- | |- | ||

| | | data-sort-value="B07" | B7 || R || MC_RESERVED1 || ? || Connected to BluRay Drive connector (CN3221) pin 49 | ||

|- | |- | ||

| | | data-sort-value="B08" | B8 || K || SB_SPI_DO || ? || Southbridge SPI Bus | ||

|- | |- | ||

| | | data-sort-value="B09" | B9 || K || SB_SPI_CS || ? || Southbridge SPI Bus | ||

|- | |- | ||

| | | data-sort-value="B10" | B10 || K || DVE_I2C_SDA || ? || Connected to Digital Video Encoder [[CXM4024R]] pin 36 | ||

|- | |- | ||

| | | data-sort-value="B11" | B11 || K || PK0 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected (CL4093) | ||

|- | |- | ||

| | | data-sort-value="B12" | B12 || E || POW_SW || ? || Connected to [[Switch_boards|Switch board]] [[CSW-001]] connector pin 4 | ||

|- | |- | ||

| | | data-sort-value="B13" | B13 || E || SB_EBUS_BRDY || ? || SS2_BRDY (StarShip2 related) | ||

|- | |- | ||

| | | data-sort-value="B14" | B14 || E || VD_CECI1 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected (CL4099) | ||

|- | |- | ||

| | | data-sort-value="B15" | B15 || E || POW_FAIL || ? || Connected to [[Components#Mitsumi_PST3642UL_.28IC_for_CMOS_System_Reset.29|Mitsumi PST3642UL]] (IC6023) pin 4. Used to monitor the state of +12V_MAIN power rail | ||

|- | |- | ||

| | | data-sort-value="B16" | B16 || data-sort-value="ZC" | <abbr title="Reset & Clock">CLK</abbr> || OSCOUT || ? || Connected to crystal 32.768Khz | ||

|- | |- | ||

| | | data-sort-value="B99" style="padding:0px" | || colspan="4" data-sort-value="ZZZ" style="padding:0px" | | ||

|- | |- | ||

| | | data-sort-value="C01" | C1 || O || MK_I2C_SDA || ? || Connected to [[Timebases#ICS_ICS1493G-18LFT|ICS1493G-18LFT]] clock generator (IC5001) pin 47 | ||

|- | |- | ||

| | | data-sort-value="C02" | C2 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#333|#fff}} AVREF2 || {{pini}} || data-sort-value="ZG" style="color:#888" | Ground | ||

|- | |- | ||

| | | data-sort-value="C03" | C3 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="C04" | C4 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="C05" | C5 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="C06" | C6 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="C07" | C7 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="C08" | C8 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="C09" | C9 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="C10" | C10 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="C11" | C11 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="C12" | C12 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="C13" | C13 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="C14" | C14 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="C15" | C15 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#333|#fff}} VSSep || {{pini}} || data-sort-value="ZG" style="color:#888" | Ground | ||

|- | |- | ||

| | | data-sort-value="C16" | C16 || data-sort-value="ZC" | <abbr title="Reset & Clock">CLK</abbr> || OSCIN || ? || Connected to crystal 32.768Khz | ||

|- | |- | ||

| | | data-sort-value="C99" style="padding:0px" | || colspan="4" data-sort-value="ZZZ" style="padding:0px" | | ||

|- | |- | ||

| | | data-sort-value="D01" | D1 || O || MK_I2C_SCL || ? || Connected to [[Timebases#ICS_ICS1493G-18LFT|ICS1493G-18LFT]] clock generator (IC5001) pin 46 | ||

|- | |- | ||

| | | data-sort-value="D02" | D2 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#f71|#fff}} VDD2 || {{pini}} || data-sort-value="ZV15" style="color:#888" | +1.5V_RSX_VDDIO | ||

|- | |- | ||

| | | data-sort-value="D03" | D3 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="D04" | D4 || O || XDR_FET_RST || {{pino}} || Connected to XDRAM chips pin C15 (XDR_RQ_RST) | ||

|- | |- | ||

| | | data-sort-value="D05" | D5 || O || XCG_EN || ? || Connected to [[Timebases#ICS_ICS9218AGLFT_.28IC_CLOCK_GEN_RAMBUS_XDR_28-TSSOP.29|ICS9218AGLFT]] (IC5002) pin 11 (switches BE_Y0_RQ_CTM/N, BE_Y1_RQ_CTM/N)<br>Connected to [[Timebases#ICS_ICS9218AGLFT_.28IC_CLOCK_GEN_RAMBUS_XDR_28-TSSOP.29|ICS9218AGLFT]] (IC5003) pin 11 (switches BE_PLL_REFCLK_P/N)<br>Connected to [[Timebases#ICS_ICS9214DGLFT_.28IC_CLOCK_GEN_RAMBUS_XDR_28-TSSOP.29|ICS9214DGLFT]] (IC5004) pin 11 (switches BE_RC_REFCLK_P/N, RSX_RC_REFCLK_P/N, SB_RC_REFCLK_P/N) | ||

|- | |- | ||

| | | data-sort-value="D06" | D6 || H || VD_CECI0 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected (CL4098) | ||

|- | |- | ||

| | | data-sort-value="D07" | D7 || H || RSX_POW_FAIL<!--RS_POW_FAIL is an official typo, the name appears several times but only one of them have the typo--> || {{pini}} || Connected to [[Regulators#OnSemi_NCP5318FTR2G_.28Two.2FThree.2FFour-Phase_Buck_CPU_Controller.29|OnSemi NCP5318FTR2G]] (IC6201) pin 7 | ||

|- | |- | ||

| | | data-sort-value="D08" | D8 || H || MUL_TRG_IN || ? || Connected to missing components (IC4003, IC4004, IC4005) pin 3 and 6 (related with BE_TRG_IN/OUT, RSX_TRG_IN/OUT, SB_TRG_IN/OUT) | ||

|- | |- | ||

| | | data-sort-value="D09" | D9 || H || SB_INT || ? || | ||

|- | |- | ||

| | | data-sort-value="D10" | D10 || F || MUL_TRG_OUT || ? || Connected to missing components (IC4006) pin 2 (related with BE_TRG_IN/OUT, RSX_TRG_IN/OUT, SB_TRG_IN/OUT) | ||

|- | |- | ||

| | | data-sort-value="D11" | D11 || F || SB_RESET || ? || Connected to [[88SA8040-TBC1]] SATA2PATA BluRay controller pin 17<br>Connected to GL852 (IC3305) USB HUB pin 38<br>Connected to Multi-card-board connector CN3219 pin 7 | ||

|- | |- | ||

| | | data-sort-value="D12" | D12 || F || PF2<br>BE_VCS_1.25_ON || ? || [[COK-001]]/[[COK-002]] PF2 (Not connected)<br>[[SEM-001]] BE_VCS_1.25_ON | ||

|- | |- | ||

| D13 || SW_1_A || Connected to [[Regulators#Mitsumi_MM1593DFBEG_.28Low-Saturation_300mA_Regulators.29|Mitsumi MM1593DFBEG]] (IC6020) pin 5 (switches +3.3V_MK_VDD) for Clock Synthesizer | | data-sort-value="D13" | D13 || F || SW_1_A || ? || Connected to [[Regulators#Mitsumi_MM1593DFBEG_.28Low-Saturation_300mA_Regulators.29|Mitsumi MM1593DFBEG]] (IC6020) pin 5 (switches +3.3V_MK_VDD) for Clock Synthesizer | ||

|- | |- | ||

| | | data-sort-value="D14" | D14 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="D15" | D15 || data-sort-value="ZC" | <abbr title="Reset & Clock">CLK</abbr> || 32KIN || ? || Connected to resistor 22ohm to pad D16 | ||

|- | |- | ||

| | | data-sort-value="D16" | D16 || data-sort-value="ZC" | <abbr title="Reset & Clock">CLK</abbr> || 32KOUT || ? || Connected to resistor 1K to +3.3V_EVER | ||

|- | |- | ||

| | | data-sort-value="D99" style="padding:0px" | || colspan="4" data-sort-value="ZZZ" style="padding:0px" | | ||

|- | |- | ||

| | | data-sort-value="E01" | E1 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#333|#fff}} VSS || {{pini}} || data-sort-value="ZG" style="color:#888" | Ground | ||

|- | |- | ||

| | | data-sort-value="E02" | E2 || N || RSX_SPI_CS || {{pino}} || Connected to [[Template:RSX pad layout 41x41|RSX]] pad AW8 (RSX SPI Bus) | ||

|- | |- | ||

| | | data-sort-value="E03" | E3 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="E04" | E4 || O || EJECT_MECHA || ? || Connected to BluRay Drive connector (CN3221) pin 56 | ||

|- | |- | ||

| | | data-sort-value="E05" | E5 || O || PO0 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected (CL4086) | ||

|- | |- | ||

| | | data-sort-value="E06" | E6 || H || HDMI_INT || {{pini}} || Connected to [[TC7WP3125FK]] (IC2501) pin 6<br> The [[TC7WP3125FK]] converts the signal originally triggered by [[Sil9132CBU]] pad E10 ? at 1.5V and converts it to 3.3V for syscon<br>The [[TC7WP3125FK]] also converts the signal RS_SPDO0 (at 1.5V) into RS_SPDO0_33 (at 3.3V) | ||

|- | |- | ||

| | | data-sort-value="E07" | E7 || H || MECHA_INT || ? || Not connected in retail PS3 models (testpad CL4102). The related SouthBridge pad is tied to GND with a 10k resistor (R3163) | ||

|- | |- | ||

| | | data-sort-value="E08" | E8 || H || MUL_CHKSTP_IN || ? || SB_CHKSTP_OUT | ||

|- | |- | ||

| | | data-sort-value="E09" | E9 || H || SYS_THR_ALRT || ? || Connected to CELL 90nm pad AP23 | ||

|- | |- | ||

| | | data-sort-value="E10" | E10 || F || MUL_CHKSTP_OUT || ? || | ||

|- | |- | ||

| | | data-sort-value="E11" | E11 || F || SB_CGRESET || ? || SB_CGRST (the name indicates that it resets the clock generator for the southbridge) | ||

|- | |- | ||

| | | data-sort-value="E12" | E12 || F || BT_WAKEON || {{pini}} || Connected to wifi board connector (CN3701) pin 30 (BT_WAKE) | ||

|- | |- | ||

| | | data-sort-value="E13" | E13 || F || PF1<br>BE_VCS_1.30_ON || ? || [[COK-001]]/[[COK-002]] PF1 (Not connected)<br>[[SEM-001]] BE_VCS_1.30_ON | ||

|- | |- | ||

| | | data-sort-value="E14" | E14 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="E15" | E15 || data-sort-value="ZE" | <abbr title="EEPROM Interface">EEP</abbr> || PP3 || ? || | ||

|- | |- | ||

| | | data-sort-value="E16" | E16 || data-sort-value="ZE" | <abbr title="EEPROM Interface">EEP</abbr> || SKB || ? || | ||

|- | |- | ||

| | | data-sort-value="E99" style="padding:0px" | || colspan="4" data-sort-value="ZZZ" style="padding:0px" | | ||

|- | |- | ||

| | | data-sort-value="F01" | F1 || N || RSX_SPI_DI || {{pini}} || Connected to [[Template:RSX pad layout 41x41|RSX]] pad BA7 (RSX SPI Bus) | ||

|- | |- | ||

| | | data-sort-value="F02" | F2 || N || RSX_SPI_DO || {{pino}} || Connected to [[Template:RSX pad layout 41x41|RSX]] pad BA6 (RSX SPI Bus) | ||

|- | |- | ||

| | | data-sort-value="F03" | F3 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="F04" | F4 || O || HDMI_RST0 || ? || Connected to [[Sil9132CBU|HDMI controller Sil9132CBU]] pad G2 ? | ||

|- | |- | ||

| | | data-sort-value="F05" | F5 || O || DISC_IN_MECHA || ? || Connected to BluRay Drive connector (CN3221) pin 55 | ||

|- | |- | ||

| | | data-sort-value="F06" | F6 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#c33|#fff}} VDD3 || {{pini}} || data-sort-value="ZV33" style="color:#888" | +3.3V_EVER | ||

|- | |- | ||

| | | data-sort-value="F07" | F7 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#c33|#fff}} AVDD || {{pini}} || data-sort-value="ZV33" style="color:#888" | +3.3V_EVER | ||

|- | |- | ||

| | | data-sort-value="F08" | F8 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#c33|#fff}} VDD3 || {{pini}} || data-sort-value="ZV33" style="color:#888" | +3.3V_EVER | ||

|- | |- | ||

| | | data-sort-value="F09" | F9 || data-sort-value="ZNC" | || data-sort-value="ZNC" | || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected | ||

|- | |- | ||

| | | data-sort-value="F10" | F10 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#c33|#fff}} VDD3 || {{pini}} || data-sort-value="ZV33" style="color:#888" | +3.3V_EVER | ||

|- | |- | ||

| | | data-sort-value="F11" | F11 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#c33|#fff}} VDDbat || {{pini}} || data-sort-value="ZV33" | Connected to <abbr title="Button cell, lithium, 20mm diameter, 2.5mm height, 3v 170mAh">CR2025 battery+</abbr> through two series diodes RB751S-40TE61 (D4008, D4007) | ||

|- | |- | ||

| | | data-sort-value="F12" | F12 || D || MK_EN || ? || Connected to [[Timebases#ICS_ICS1493G-18LFT|ICS1493G-18LFT]] clock generator (IC5001) pin 16 | ||

|- | |- | ||

| | | data-sort-value="F13" | F13 || D || SW_5_B || ? || Connected to [[Regulators#Rohm_BD3520FVM-TR_.28Single_channel_Regulator_Driver_IC.29|Rohm BD3520FVM-TR]] (IC6200) pin 3 (switches +1.2V_RSX_VDDR) | ||

|- | |- | ||

| | | data-sort-value="F14" | F14 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="F15" | F15 || data-sort-value="ZE" | <abbr title="EEPROM Interface">EEP</abbr> || PP0 || ? || | ||

|- | |- | ||

| | | data-sort-value="F16" | F16 || data-sort-value="ZE" | <abbr title="EEPROM Interface">EEP</abbr> || CSB || ? || | ||

|- | |- | ||

| | | data-sort-value="F99" style="padding:0px" | || colspan="4" data-sort-value="ZZZ" style="padding:0px" | | ||

|- | |- | ||

| | | data-sort-value="G01" | G1 || N || RSX_SPI_CLK || {{pino}} || Connected to [[Template:RSX pad layout 41x41|RSX]] pad AY8 (RSX SPI Bus) | ||

|- | |- | ||

| | | data-sort-value="G02" | G2 || N || RSX_RESET || {{pino}} || Connected to [[Template:RSX pad layout 41x41|RSX]] pads AW5 (RESET) and AV6 (CGRESET) | ||

|- | |- | ||

| | | data-sort-value="G03" | G3 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="G04" | G4 || O || HDMI_RST1 || ? || Not connected ? (it seems to be a secondary reset signal for [[Sil9132CBU|HDMI controller Sil9132CBU]] never used in retail PS3 models) | ||

|- | |- | ||

| | | data-sort-value="G05" | G5 || O || SW_AVCG<br>PO5 || ? || Connected to [[Timebases#ICS_ICS422AG-07LFT_.28IC_CLOCK_GEN_RSX_AV_CLK_24-TSSOP.29|ICS422AG-07LFT]] (IC2102) pin 12 (switches RSX_AVCLK0, RSX_AVCLK1, RSX_AVCLK2, RSX_AVCLK3) clocks for [[RSX]] and indirectly for EEGS<->RDRAM | ||

|- | |- | ||

| | | data-sort-value="G06" | G6 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#333|#fff}} AVSS || {{pini}} || data-sort-value="ZG" style="color:#888" | Ground | ||

|- | |- | ||

| | | data-sort-value="G06" | G7 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#333|#fff}} VSS || {{pini}} || data-sort-value="ZG" style="color:#888" | Ground | ||

|- | |- | ||

| | | data-sort-value="G08" | G8 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#333|#fff}} VSS || {{pini}} || data-sort-value="ZG" style="color:#888" | Ground | ||

|- | |- | ||

| | | data-sort-value="G09" | G9 || data-sort-value="ZNC" | || data-sort-value="ZNC" | || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected | ||

|- | |- | ||

| | | data-sort-value="G10" | G10 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#333|#fff}} VSS || {{pini}} || data-sort-value="ZG" style="color:#888" | Ground | ||

|- | |- | ||

| | | data-sort-value="G11" | G11 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#c33|#fff}} VDDep || {{pini}} || data-sort-value="ZV33" style="color:#888" | +3.3V_EVER | ||

|- | |- | ||

| | | data-sort-value="G12" | G12 || D || BEVRM_VID4 || ? || Connected to [[Regulators#OnSemi_NCP5318FTR2G_.28Two.2FThree.2FFour-Phase_Buck_CPU_Controller.29|OnSemi NCP5318FTR2G]] (IC6103) pin 3 | ||

|- | |- | ||

| | | data-sort-value="G13" | G13 || D || BEVRM_VID5 || ? || Connected to [[Regulators#OnSemi_NCP5318FTR2G_.28Two.2FThree.2FFour-Phase_Buck_CPU_Controller.29|OnSemi NCP5318FTR2G]] (IC6103) pin 30 | ||

|- | |- | ||

| | | data-sort-value="G14" | G14 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="G15" | G15 || data-sort-value="ZE" | <abbr title="EEPROM Interface">EEP</abbr> || PP2 || ? || | ||

|- | |- | ||

| | | data-sort-value="G16" | G16 || data-sort-value="ZE" | <abbr title="EEPROM Interface">EEP</abbr> || DI || ? || | ||

|- | |- | ||

| | | data-sort-value="G99" style="padding:0px" | || colspan="4" data-sort-value="ZZZ" style="padding:0px" | | ||

|- | |- | ||

| | | data-sort-value="H01" | H1 || N || PN5 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected (CL4084) | ||

|- | |- | ||

| | | data-sort-value="H02" | H2 || N || PN6 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected (CL4012) | ||

|- | |- | ||

| | | data-sort-value="H03" | H3 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="H04" | H4 || L || PL2 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected | ||

|- | |- | ||

| | | data-sort-value="H05" | H5 || L || PL1 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected | ||

|- | |- | ||

| | | data-sort-value="H06" | H6 || L || PL0 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected | ||

|- | |- | ||

| | | data-sort-value="H07" | H7 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#e63|#fff}} DVDD || {{pini}} || data-sort-value="ZV18" style="color:#888" | +1.8V_EVER | ||

|- | |- | ||

| | | data-sort-value="H08" | H08 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="H09" | H09 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="H10" | H10 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#c33|#fff}} VDD3 || {{pini}} || data-sort-value="ZV33" style="color:#888" | +3.3V_EVER | ||

|- | |- | ||

| | | data-sort-value="H11" | H11 || data-sort-value="ZC" | <abbr title="Reset & Clock">CLK</abbr> || TESTMODE || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected | ||

|- | |- | ||

| | | data-sort-value="H12" | H12 || D || BEVRM_VID2 || ? || Connected to [[Regulators#OnSemi_NCP5318FTR2G_.28Two.2FThree.2FFour-Phase_Buck_CPU_Controller.29|OnSemi NCP5318FTR2G]] (IC6103) pin 1 | ||

|- | |- | ||

| | | data-sort-value="H13" | H13 || D || BEVRM_VID3 || ? || Connected to [[Regulators#OnSemi_NCP5318FTR2G_.28Two.2FThree.2FFour-Phase_Buck_CPU_Controller.29|OnSemi NCP5318FTR2G]] (IC6103) pin 2 | ||

|- | |- | ||

| | | data-sort-value="H14" | H14 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="H15" | H15 || data-sort-value="ZE" | <abbr title="EEPROM Interface">EEP</abbr> || PP1 || ? || | ||

|- | |- | ||

| | | data-sort-value="H16" | H16 || data-sort-value="ZE" | <abbr title="EEPROM Interface">EEP</abbr> || DO || ? || | ||

|- | |- | ||

| | | data-sort-value="H99" style="padding:0px" | || colspan="4" data-sort-value="ZZZ" style="padding:0px" | | ||

|- | |- | ||

| | | data-sort-value="J01" | J1 || N || RSX_FLDO1 || {{pini}} || Connected to [[Template:RSX pad layout 41x41|RSX]] pad AM40 | ||

|- | |- | ||

| | | data-sort-value="J02" | J2 || N || RSX_INT || {{pini}} || Connected to [[Template:RSX pad layout 41x41|RSX]] pad AY7 | ||

|- | |- | ||

| | | data-sort-value="J03" | J3 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="J04" | J4 || L || PL4 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected | ||

|- | |- | ||

| | | data-sort-value="J05" | J5 || L || PL3 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected | ||

|- | |- | ||

| | | data-sort-value="J06" | J6 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#c33|#fff}} VDD3 || {{pini}} || data-sort-value="ZV33" style="color:#888" | +3.3V_EVER | ||

|- | |- | ||

| | | data-sort-value="J07" | J7 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#e63|#fff}} DVDD || {{pini}} || data-sort-value="ZV18" style="color:#888" | +1.8V_EVER | ||

|- | |- | ||

| | | data-sort-value="J08" | J08 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="J09" | J09 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="J10" | J10 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#e63|#fff}} DVDD || {{pini}} || data-sort-value="ZV18" style="color:#888" | +1.8V_EVER | ||

|- | |- | ||

| | | data-sort-value="J11" | J11 || data-sort-value="ZC" | <abbr title="Reset & Clock">CLK</abbr> || RST || ? || Connected to [[Service_Connectors#CN4009| service connector]] (CN4009) pin 8 | ||

|- | |- | ||

| | | data-sort-value="J12" | J12 || D || BEVRM_VID0 || ? || Connected to [[Regulators#OnSemi_NCP5318FTR2G_.28Two.2FThree.2FFour-Phase_Buck_CPU_Controller.29|OnSemi NCP5318FTR2G]] (IC6103) pin 31 | ||

|- | |- | ||

| | | data-sort-value="J13" | J13 || D || BEVRM_VID1 || ? || Connected to [[Regulators#OnSemi_NCP5318FTR2G_.28Two.2FThree.2FFour-Phase_Buck_CPU_Controller.29|OnSemi NCP5318FTR2G]] (IC6103) pin 32 | ||

|- | |- | ||

| | | data-sort-value="J14" | J14 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="J15" | J15 || data-sort-value="ZE" | <abbr title="EEPROM Interface">EEP</abbr> || WCB || ? || | ||

|- | |- | ||

| | | data-sort-value="J16" | J16 || data-sort-value="ZE" | <abbr title="EEPROM Interface">EEP</abbr> || RBB || ? || | ||

|- | |- | ||

| | | data-sort-value="J99" style="padding:0px" | || colspan="4" data-sort-value="ZZZ" style="padding:0px" | | ||

|- | |- | ||

| | | data-sort-value="K01" | K1 || N || VD_VINT0 || {{pini}} || Connected to [[RSX]] pad AR22 ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="K02" | K2 || N || VD_VINT1 || {{pini}} || Connected to [[RSX]] pad AL38 ([[Template:RSX pad layout 41x41|41x41 layout]]) | ||

|- | |- | ||

| | | data-sort-value="K03" | K3 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="K04" | K4 || L || PL6 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected | ||

|- | |- | ||

| | | data-sort-value="K05" | K5 || L || PL5 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected | ||

|- | |- | ||

| | | data-sort-value="K06" | K6 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#333|#fff}} VSSF || {{pini}} || data-sort-value="ZG" style="color:#888" | Ground | ||

|- | |- | ||

| | | data-sort-value="K07" | K7 || data-sort-value="ZJ" | JTAG || JTDI || ? || Connected to [[Service_Connectors#CN4009| service connector]] (CN4009) pin 3 | ||

|- | |- | ||

| | | data-sort-value="K08" | K8 || data-sort-value="ZJ" | JTAG || JTCK || ? || Connected to [[Service_Connectors#CN4009| service connector]] (CN4009) pin 5 | ||

|- | |- | ||

| | | data-sort-value="K09" | K9 || data-sort-value="ZJ" | JTAG || JTDO || ? || Connected to [[Service_Connectors#CN4009| service connector]] (CN4009) pin 6 | ||

|- | |- | ||

| | | data-sort-value="K10" | K10 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#e63|#fff}} DVDD || {{pini}} || data-sort-value="ZV18" style="color:#888" | +1.8V_EVER | ||

|- | |- | ||

| | | data-sort-value="K11" | K11 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#333|#fff}} VSSF || {{pini}} || data-sort-value="ZG" style="color:#888" | Ground | ||

|- | |- | ||

| | | data-sort-value="K12" | K12 || C || I2CBUS_EN || ? || Connected to [[Components#Toshiba_TC7WB66FK.28TE85R.29_.28low_on-resistance.2C_high-speed_CMOS2-bit_bus_switch.29|Toshiba TC7WB66FK]] pins 3 and 7 (IC5005 on [[SEM-001]]) through 1K resistor (in COK-001 the resistor is missing, a.k.a. this syscon line is N/C). This chip "duplicates" the MK_I2C_SCL/MK_I2C_SDA bus into a secondary XCG_I2C_SCL/XCG_I2C_SDA bus for the clock reference chip/s | ||

|- | |- | ||

| | | data-sort-value="K13" | K13 || C || PC7 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected (CL4085) | ||

|- | |- | ||

| | | data-sort-value="K14" | K14 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="K15" | K15 || data-sort-value="ZE" | <abbr title="EEPROM Interface">EEP</abbr> || PI6 || ? || | ||

|- | |- | ||

| | | data-sort-value="K16" | K16 || data-sort-value="ZE" | <abbr title="EEPROM Interface">EEP</abbr> || PI7 || ? || | ||

|- | |- | ||

| | | data-sort-value="K99" style="padding:0px" | || colspan="4" data-sort-value="ZZZ" style="padding:0px" | | ||

|- | |- | ||

| | | data-sort-value="L01" | L1 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#333|#fff}} VSS || {{pini}} || data-sort-value="ZG" style="color:#888" | Ground | ||

|- | |- | ||

| | | data-sort-value="L02" | L2 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#f93|#fff}} VDD0 || {{pini}} || data-sort-value="ZV12" style="color:#888" | +1.2V_MC2_VDDIO | ||

|- | |- | ||

| | | data-sort-value="L03" | L3 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="L04" | L4 || L<!--the name "Port N" is an official typo--> || PL8 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected | ||

|- | |- | ||

| | | data-sort-value="L05" | L5 || L || PL7 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected | ||

|- | |- | ||

| | | data-sort-value="L06" | L6 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#c33|#fff}} VDDF || {{pini}} || data-sort-value="ZV33" style="color:#888" | +3.3V_EVER | ||

|- | |- | ||

| | | data-sort-value="L07" | L7 || data-sort-value="ZJ" | JTAG || JNTRST || ? || Connected to [[Service_Connectors#CN4009| service connector]] (CN4009) pin 2 ? | ||

|- | |- | ||

| | | data-sort-value="L08" | L8 || data-sort-value="ZJ" | JTAG || JRTCK || ? || Connected to [[Service_Connectors#CN4009| service connector]] (CN4009) pin 4 | ||

|- | |- | ||

| | | data-sort-value="L09" | L9 || data-sort-value="ZJ" | JTAG || JTMS || ? || Connected to [[Service_Connectors#CN4009| service connector]] (CN4009) pin 7 | ||

|- | |- | ||

| | | data-sort-value="L10" | L10 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#e63|#fff}} DVDD || {{pini}} || data-sort-value="ZV18" style="color:#888" | +1.8V_EVER | ||

|- | |- | ||

| | | data-sort-value="L11" | L11 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#e63|#fff}} DVDD || {{pini}} || data-sort-value="ZV18" style="color:#888" | +1.8V_EVER | ||

|- | |- | ||

| | | data-sort-value="L12" | L12 || C || RSXVRM_VID4 || {{pino}} || Connected to [[Regulators#OnSemi_NCP5318FTR2G_.28Two.2FThree.2FFour-Phase_Buck_CPU_Controller.29|OnSemi NCP5318FTR2G]] (IC6201) pin 3 | ||

|- | |- | ||

| | | data-sort-value="L13" | L13 || C || RSXVRM_VID5 || {{pino}} || Connected to [[Regulators#OnSemi_NCP5318FTR2G_.28Two.2FThree.2FFour-Phase_Buck_CPU_Controller.29|OnSemi NCP5318FTR2G]] (IC6201) pin 30 | ||

|- | |- | ||

| | | data-sort-value="L14" | L14 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="L15" | L15 || I || DISC_CHUCK || ? || Connected to BluRay Drive connector (CN3221) pin 54 | ||

|- | |- | ||

| | | data-sort-value="L16" | L16 || I || SW_PCI || ? || Connected to [[Regulators#Mitsumi_MM1591FFBEG_.28Low-Saturation_300mA_Regulators.29 | Mitsumi MM1591FFBEG]] (IC6021) pin 5 (switches +1.5V_BRIDGE) for the PS2 bridge [[CXD9208GP]]<br>Connected to [[Regulators#Mitsumi_MM1593DFBEG_.28Low-Saturation_300mA_Regulators.29 | Mitsumi MM1593DFBEG]] (IC6022) pin 5 (switches +3.3V_BRIDGE) for the PS2 bridge [[CXD9208GP]]<br>Connected to PCI service connector pin 80 | ||

|- | |- | ||

| | | data-sort-value="L99" style="padding:0px" | || colspan="4" data-sort-value="ZZZ" style="padding:0px" | | ||

|- | |- | ||

| | | data-sort-value="M01" | M1 || M || BE_SPI_DI || ? || Connected to CELL 90nm pad AR13 (SPI Bus) | ||

|- | |- | ||

| | | data-sort-value="M02" | M2 || M || BE_SPI_CS || ? || Connected to CELL 90nm pad AP13 (SPI Bus) | ||

|- | |- | ||

| | | data-sort-value="M03" | M3 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="M04" | M4 || A || PA0 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected (CL4092) | ||

|- | |- | ||

| | | data-sort-value="M05" | M5 || A || WLAN_RESET || {{pino}} || Connected to wifi board connector (CN3701) pin 29 (11G_RESET) | ||

|- | |- | ||

| | | data-sort-value="M06" | M6 || A || PA4 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected (CL4087) | ||

|- | |- | ||

| | | data-sort-value="M07" | M7 || A || POW_LED || ? || Connected to [[Switch_boards|Switch board]] [[CSW-001]] connector pin 6 | ||

|- | |- | ||

| | | data-sort-value="M08" | M8 || G || FANPWM1 || ? || Secondary fan output (non-retail PS3 models only) | ||

|- | |- | ||

| | | data-sort-value="M09" | M9 || G || BUZZER || {{pino}} || Connected to Buzzer (BZ4001) through transistor DTC143ZUA-T106 (Q4014) | ||

|- | |- | ||

| | | data-sort-value="M10" | M10 || G || XDR_FET_VREF || {{pino}} || Connected to transistor DTC144EUA-T106 (Q4008). Switches XDR_RQ_VREF_FET | ||

|- | |- | ||

| | | data-sort-value="M11" | M11 || G || SW_ATA || ? || Connected to UMH2NTN dual transistor (Q6009) pin 2 (switches +12V_BD)<br>Connected to UMH2NTN dual transistor (Q6009) pin 5 (switches +5V_BD)<br>Connected to UMH2NTN dual transistor (Q6006) pin 2 (switches +5V_HDD) | ||

|- | |- | ||

| | | data-sort-value="M12" | M12 || C || RSXVRM_VID2 || {{pino}} || Connected to [[Regulators#OnSemi_NCP5318FTR2G_.28Two.2FThree.2FFour-Phase_Buck_CPU_Controller.29|OnSemi NCP5318FTR2G]] (IC6201) pin 1 | ||

|- | |- | ||

| | | data-sort-value="M13" | M13 || C || RSXVRM_VID3 || {{pino}} || Connected to [[Regulators#OnSemi_NCP5318FTR2G_.28Two.2FThree.2FFour-Phase_Buck_CPU_Controller.29|OnSemi NCP5318FTR2G]] (IC6201) pin 2 | ||

|- | |- | ||

| | | data-sort-value="M14" | M14 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| | | data-sort-value="M15" | M15 || I || SW_2 || ? || Connected to [[Regulators#Texas_Instruments_TPS51117PWRG4_.281.8V_to_28V_Input_Sync._Step_Down_Controller_10A_0.75_V_to_5.5_V.29|Texas Instruments TPS51117PWRG4]] (IC6302) pin 1 (switches +1.8V_VDD_MEM) | ||

|- | |- | ||

| | | data-sort-value="M16" | M16 || I || DISC_PHOT_LED || ? || Connected to BluRay Drive connector (CN3221) pin 53 | ||

|- | |- | ||

| | | data-sort-value="M99" style="padding:0px" | || colspan="4" data-sort-value="ZZZ" style="padding:0px" | | ||

|- | |- | ||

| | | data-sort-value="N01" | N1 || M || BE_SPI_CLK || ? || Connected to CELL 90nm pad AY13 (SPI Bus) | ||

|- | |- | ||

| | | data-sort-value="N02" | N2 || M || BE_SPI_DO || ? || Connected to CELL 90nm pad AV13 (SPI Bus) | ||

|- | |- | ||

| | | data-sort-value="N03" | N3 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | ||

|- | |- | ||

| E2 || | | data-sort-value="N04" | N4 || A || SW_5_A || ? || Connected to [[Regulators#OnSemi_NCP5318FTR2G_.28Two.2FThree.2FFour-Phase_Buck_CPU_Controller.29|OnSemi NCP5318FTR2G]] (IC6201) pin 29<br>Connected to [[Components#Toshiba_TC7SG08FU_.282_Input_AND_Gate.29|Toshiba TC7SG08FU]] (IC6204) pin 1<br>Switches +1.2V_RSX_VDDC | ||

|- | |||

| data-sort-value="N05" | N5 || A || BT_RESET || {{pino}} || Connected to wifi board connector (CN3701) pin 10 (SYSCON_RST) | |||

|- | |||

| data-sort-value="N06" | N6 || A || AUDIO_MUTE || ? || Connected to transistor DTA144EUA-T106 (Q2404). Switches [[Components#Cirrus_CX4351-CZZR|Cirrus CX4351-CZZR]] pin 18 (AOUTA) left audio channel and pin 15 (AOUTB) right audio channel, that are connected to [[Connectors#AV_Multi_Out_pinout_-_CN2401_12P|MultiAV connector]] pin 11 (AUL) and pin9 (AUR) respectivelly | |||

|- | |||

| data-sort-value="N07" | N7 || A || STBY_LED || ? || Connected to [[Switch_boards|Switch board]] [[CSW-001]] connector pin 7 | |||

|- | |||

| data-sort-value="N08" | N8 || G || FANPWM0 || ? || Primary fan output (all PS3 models) | |||

|- | |||

| data-sort-value="N09" | N9 || G || SW_PWM || ? || Connected to [[Switch_boards|Switch board]] [[CSW-001]] connector pin 2 | |||

|- | |||

| data-sort-value="N10" | N10 || G || XDR_FET_SCK || {{pino}} || Connected to transistor SST222AT116 (Q1302) BE_RQ_SCK_BJT | |||

|- | |||

| data-sort-value="N11" | N11 || G || SW_4_A || {{pino}} || Connected to wifi board connector (CN3701) pin 9 (11G_PWR_EN)<br>Connected to base pin of transistor UMH2NTN (Q3501) who switches IC3502 pin 5, and IC3501 pin 3 (+1.2V_ESW, +1.9V_ESW, +3.3V_ESW for Ethernet Controller) | |||

|- | |||

| data-sort-value="N12" | N12 || C || RSXVRM_VID0 || {{pino}} || Connected to [[Regulators#OnSemi_NCP5318FTR2G_.28Two.2FThree.2FFour-Phase_Buck_CPU_Controller.29|OnSemi NCP5318FTR2G]] (IC6201) pin 31 | |||

|- | |||

| data-sort-value="N13" | N13 || C || RSXVRM_VID1 || {{pino}} || Connected to [[Regulators#OnSemi_NCP5318FTR2G_.28Two.2FThree.2FFour-Phase_Buck_CPU_Controller.29|OnSemi NCP5318FTR2G]] (IC6201) pin 32 | |||

|- | |||

| data-sort-value="N14" | N14 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | |||

|- | |||

| data-sort-value="N15" | N15 || I || BACKUP_MODE || ? || Connected to [[Service_Connectors#CN4009| service connector]] (CN4009) pin 14 | |||

|- | |||

| data-sort-value="N16" | N16 || I || DIAG_MODE || ? || Connected to [[Service_Connectors#CN4009| service connector]] (CN4009) pin 13 | |||

|- | |||

| data-sort-value="N99" style="padding:0px" | || colspan="4" data-sort-value="ZZZ" style="padding:0px" | | |||

|- | |||

| data-sort-value="P01" | P1 || M || BE_POWGOOD || ? || Connected to CELL 90nm pad AV20 | |||

|- | |||

| data-sort-value="P02" | P2 || M || BE_RESET || ? || Connected to CELL 90nm pad AW20 | |||

|- | |||

| data-sort-value="P03" | P3 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | |||

|- | |||

| data-sort-value="P04" | P4 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | |||

|- | |||

| data-sort-value="P05" | P5 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | |||

|- | |||

| data-sort-value="P06" | P6 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | |||

|- | |||

| data-sort-value="P07" | P7 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | |||

|- | |||

| data-sort-value="P08" | P8 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | |||

|- | |||

| data-sort-value="P09" | P9 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | |||

|- | |||

| data-sort-value="P10" | P10 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | |||

|- | |||

| data-sort-value="P11" | P11 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | |||

|- | |||

| data-sort-value="P12" | P12 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | |||

|- | |||

| data-sort-value="P13" | P13 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | |||

|- | |||

| data-sort-value="P14" | P14 || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" {{cellcolors|#eee|#888}} N/A || data-sort-value="ZNA" style="color:#888" | Missing pad | |||

|- | |||

| data-sort-value="P15" | P15 || P || UART0_RxD || ? || Connected to [[Service_Connectors#CN4009| service connector]] (CN4009) pin 10 (Serial Receive) | |||

|- | |||

| data-sort-value="P16" | P16 || P || UART0_TxD || ? || Connected to [[Service_Connectors#CN4009| service connector]] (CN4009) pin 11 (Serial Transmit) | |||

|- | |||

| data-sort-value="P99" style="padding:0px" | || colspan="4" data-sort-value="ZZZ" style="padding:0px" | | |||

|- | |||

| data-sort-value="R01" | R1 || M || PM7 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected (CL4011) | |||

|- | |||

| data-sort-value="R02" | R2 || M || PM6 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected (CL4010) | |||

|- | |||

| data-sort-value="R03" | R3 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#f93|#fff}} VDD1 || {{pini}} || data-sort-value="ZV12" style="color:#888" | +1.2V_MC2_VDDIO | |||

|- | |||

| data-sort-value="R04" | R4 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#333|#fff}} AVSUO || {{pini}} || data-sort-value="ZG" style="color:#888" | Ground | |||

|- | |||

| data-sort-value="R05" | R5 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#c33|#fff}} AVDUO || {{pini}} || data-sort-value="ZV33" style="color:#888" | +3.3V_EVER | |||

|- | |||

| data-sort-value="R06" | R6 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#333|#fff}} VSS || {{pini}} || data-sort-value="ZG" style="color:#888" | Ground | |||

|- | |||

| data-sort-value="R07" | R7 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#e63|#fff}} DVDD || {{pini}} || data-sort-value="ZV18" style="color:#888" | +1.8V_EVER | |||

|- | |||

| data-sort-value="R08" | R8 || Q || RSX_FBVDD_SEL || {{pino}} || Connected to [[Components#Texas_Instruments_SN105233DBTR|Texas Instruments SN105233DBTR]] (IC6301) through transistor/s | |||

|- | |||

| data-sort-value="R09" | R9 || Q || PQ1 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected (CL4020) | |||

|- | |||

| data-sort-value="R10" | R10 || Q || RMC_IN || ? || Connected to [[Switch_boards|Switch board]] [[CSW-001]] connector pin 3<br> Connected to [[Service_Connectors#CN4009| service connector]] (CN4009) pin 17 | |||

|- | |||

| data-sort-value="R11" | R11 || B || VD_CECO0 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected (CL4100) | |||

|- | |||

| data-sort-value="R12" | R12 || B || SW_3 || ? || Connected to [[Regulators#Rohm_BD3520FVM-TR_.28Single_channel_Regulator_Driver_IC.29|Rohm BD3520FVM-TR]] (IC6305) pin 3 (switches +1.2V_SB_VDDC and +1.2V_SB_VDDR) | |||

|- | |||

| data-sort-value="R13" | R13 || B || SW_1_B || ? || Connected to [[Regulators#Mitsumi_MM1562ZFBE_.28Low-Saturation_500mA_Regulators.29 | Mitsumi MM1562ZFBE]] (IC6013) pin 5 (switches +2.5V_LREG_XCG_500_MEM)<br>Connected to [[Components#Toshiba_TC7WB66FK.28TE85R.29_.28low_on-resistance.2C_high-speed_CMOS2-bit_bus_switch.29|Toshiba TC7WB66FK]] (IC5005) pins 3 and 7, and to (IC5006) pin 4, through 1K resistor. The TC7WB66FK chip "duplicates" the MK_I2C_SCL/MK_I2C_SDA bus into a secondary XCG_I2C_SCL/XCG_I2C_SDA bus for the clock reference chip/s<br>Analog Voltage for the core PLL of IC5004, Clock Generator used to support the Rambus XDR memory subsystem and Redwood logic interface. | |||

|- | |||

| data-sort-value="R14" | R14 || B || SW_7_A || ? || Connected to [[Regulators#OnSemi_NCP5318FTR2G_.28Two.2FThree.2FFour-Phase_Buck_CPU_Controller.29|OnSemi NCP5318FTR2G]] (IC6103) pin 29<br>Connected to [[Components#Toshiba_TC7SG08FU_.282_Input_AND_Gate.29|Toshiba TC7SG08FU]] (IC6107) pin 1<br>Switches +1.0V_BE_VDDC<br>Cell BE core voltage supply (VDD) then VCS (the core array voltage). Note, the VID values stored on the CELL itself are not available to be read yet. So the default VID of the VRM is used until then. | |||

|- | |||

| data-sort-value="R15" | R15 || P || HDMI_I2C_SDA || ? || Connected to [[Sil9132CBU|HDMI controller Sil9132CBU]] pad D2 | |||

|- | |||

| data-sort-value="R16" | R16 || P || HDMI_I2C_SCL || ? || Connected to [[Sil9132CBU|HDMI controller Sil9132CBU]] pad E2 | |||

|- | |||

| data-sort-value="R99" style="padding:0px" | || colspan="4" data-sort-value="ZZZ" style="padding:0px" | | |||

|- | |||

| data-sort-value="T01" | T1 || data-sort-value="ZNC" | || data-sort-value="ZNC" | || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected | |||

|- | |||

| data-sort-value="T02" | T2 || M || BE_INT || ? || Connected to CELL 90nm pad AW19 | |||

|- | |||

| data-sort-value="T03" | T3 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#333|#fff}} VSS || {{pini}} || data-sort-value="ZG" style="color:#888" | Ground | |||

|- | |||

| data-sort-value="T04" | T4 || data-sort-value="ZC" | <abbr title="Reset & Clock">CLK</abbr> || XTAL || ? || Connected to crystal 16.9344Mhz | |||

|- | |||

| data-sort-value="T05" | T5 || data-sort-value="ZC" | <abbr title="Reset & Clock">CLK</abbr> || EXTAL || ? || Connected to crystal 16.9344Mhz | |||

|- | |||

| data-sort-value="T06" | T6 || data-sort-value="ZP" | <abbr title="Power port>PWR</abbr> || {{cellcolors|#333|#fff}} VSS || {{pini}} || data-sort-value="ZG" style="color:#888" | Ground | |||

|- | |||

| data-sort-value="T07" | T7 || data-sort-value="ZC" | <abbr title="Reset & Clock">CLK</abbr> || XXTALO || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected (CL4040) | |||

|- | |||

| data-sort-value="T08" | T8 || Q || THR_I2C_SCL || {{pino}} || Connected to [[Thermal#Temperature_Monitors]] | |||

|- | |||

| data-sort-value="T09" | T9 || Q || THR_I2C_SDA || {{pinio}} || Connected to [[Thermal#Temperature_Monitors]] | |||

|- | |||

| data-sort-value="T10" | T10 || Q || PQ4 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected (CL4021) | |||

|- | |||

| data-sort-value="T11" | T11 || Q || PQ5 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected (CL4022) | |||

|- | |||

| data-sort-value="T12" | T12 || B || VD_CECO1 || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected (CL4101) | |||

|- | |||

| data-sort-value="T13" | T13 || B || SW_4_B || ? || Connected to 88E6108 ethernet controller (IC3503) pin 94 (signal named P3_ENABLE_PD)<br>Connected to (Q6003) transistor (switches +3.3V_SB_VDDIO)<br>Connected to [[Regulators#OnSemi_NCP511SN25T1G_.282.5V_150_mA_CMOS_Low_Iq_Low-Dropout_Voltage_Regulator.29 | OnSemi NCP511SN25T1G]] (IC6011) pin 3 (switches +2.5V_SB_PLL_VDDC)<br>Connected to [[Regulators#Mitsumi_MM1591JFBEG_.28Low-Saturation_300mA_Regulators.29 | Mitsumi MM1591JFBEG]] (IC6014) pin 5 (switches +1.8V_SB_PERI)<br>Connected to UMH2NTN dual transistor (Q6006) pin 5 (switches +5V_USB) | |||

|- | |||

| data-sort-value="T14" | T14 || B || SW_6 || ? || Connected to [[Regulators#Rohm_BD3520FVM-TR_.28Single_channel_Regulator_Driver_IC.29|Rohm BD3520FVM-TR]] (IC6303) pin 3 (switches +1.2V_YC_RC_VDDIO)<br>Connected to [[Regulators#Mitsumi_MM3141CNRE_.28150mA_Regulator_Monolithic.29 | Mitsumi MM3141CNRE]] (IC6012) pin 3 (switches +1.2V_MC2_VDDIO)<br>I/O voltage supplies, VDD_IO for [[CELL]], [[RSX]] and [[South Bridge]] | |||

|- | |||

| data-sort-value="T15" | T15 || B || SW_8_A || ? || Connected to [[Regulators#Rohm_BD3504FVM-TR_.28Single_channel_Regulator_Driver_IC.29 | Rohm BD3504FVM-TR]] (IC6304) pin 3 (switches +1.5V_YC_RC_VDDA)<br>Connected to [[Regulators#Texas_Instruments_TPS73101DBVRG4_.28Single_Output_LDO.2C_150mA.2C_Adj._1.2-5.5V_SOT23-5.29 | Texas Instruments TPS73101DBVRG4]] (IC6007) pin 3 (switches +1.6V_BE_VDDA) | |||

|- | |||

| data-sort-value="T16" | T16 || data-sort-value="ZNC" | || data-sort-value="ZNC" | || {{pinnc}} || data-sort-value="ZNC" style="color:#888" | Not Connected | |||

|}</div><noinclude>[[Category:Templates]]</noinclude> | |}</div><noinclude>[[Category:Templates]]</noinclude> | ||

Latest revision as of 03:43, 16 November 2022

| Pad | Port | Name | Type | Description |

|---|---|---|---|---|

| A1 | Not Connected | |||

| A2 | J | DISC_IN | ? | Connected to BluRay Drive connector (CN3221) pin 52 |

| A3 | J | SW_0 | ? | Connected to Fujitsu MB39A116PFT (IC6003) pin 9 (switches +5V_MISC) Connected to Fujitsu MB39A116PFT (IC6003) pin 10 (switches +3.3V_MISC) Connected to Texas Instruments SN105233DBTR (IC6301) pin 10 (switches +1.7_MISC) |

| A4 | J | SW_8_C | ? | Connected to Texas Instruments SN105233DBTR (IC6301) pin 9 (switches +1.8V_RSX_FBVDDQ) Connected to OnSemi NCP511SN18T1 (IC6008) pin 3 (switches +1.8V_RSX_PLL_VDD) |

| A5 | J | DISC_OUT12_SW | ? | Connected to BluRay Drive connector (CN3221) pin 58 |

| A6 | R | MC_RESERVED2 | ? | Not connected to BluRay Drive because a missing resistor (R4080). BD_LED |

| A7 | R | MC_ALIVE | ? | Connected to BluRay Drive connector (CN3221) pin 47 |

| A8 | K | SB_SPI_CLK | ? | Southbridge SPI Bus |

| A9 | K | SB_SPI_DI | ? | Southbridge SPI Bus |

| A10 | K | DVE_I2C_SCL | ? | Connected to Digital Video Encoder CXM4024R pin 35 |

| A11 | K | ACDC_STBY | ? | Connected to Power Supply (small connector). This signal enables +12V_MAIN power rail (big prongs) |

| A12 | E | EJECT_SW | ? | Connected to Switch board CSW-001 connector pin 5 |

| A13 | E | SB_EBUS_RESET | ? | SS2_RESET (StarShip2 related), not connected because a missing resistor (R4135) ? |

| A14 | E | PE3 | Not Connected (CL4094) | |

| A15 | E | BE_POW_FAIL | ? | Connected to OnSemi NCP5318FTR2G (IC6103) pin 7 |

| A16 | Not Connected | |||

| B1 | PWR | AVREF1 | +3.3V_EVER | |

| B2 | J | DISC_OUT8_SW | ? | Connected to BluRay Drive connector (CN3221) pin 57 |

| B3 | J | PJ3 | Not Connected (CL4089) | |

| B4 | J | SW_8_B | ? | Connected to Mitsumi MM1561JFBE (IC2408) pin 5 (switches +1.8V_ANA) Connected to Mitsumi MM1593DFBEG (IC2407) pin 5 (switches +3.3V_ANA) Connected to transistor DTC144EUA-T106 (Q2401) base pin (switches +5V_ANA ?) Connected to OnSemi NCP511SN15T1G (IC6019) pin 3 (switches +1.5V_AVCG_VDDIO) Connected to Rohm BD3521FVM-TR (IC6017) pin 3 (switches +1.5V_RSX_VDDIO) |

| B5 | J | DVE_RST | ? | Connected to Digital Video Encoder CXM4024R pin 31 ? |

| B6 | R | MC_P_OFF_REQ | ? | Connected to BluRay Drive connector (CN3221) pin 48 |

| B7 | R | MC_RESERVED1 | ? | Connected to BluRay Drive connector (CN3221) pin 49 |

| B8 | K | SB_SPI_DO | ? | Southbridge SPI Bus |

| B9 | K | SB_SPI_CS | ? | Southbridge SPI Bus |

| B10 | K | DVE_I2C_SDA | ? | Connected to Digital Video Encoder CXM4024R pin 36 |

| B11 | K | PK0 | Not Connected (CL4093) | |

| B12 | E | POW_SW | ? | Connected to Switch board CSW-001 connector pin 4 |

| B13 | E | SB_EBUS_BRDY | ? | SS2_BRDY (StarShip2 related) |

| B14 | E | VD_CECI1 | Not Connected (CL4099) | |

| B15 | E | POW_FAIL | ? | Connected to Mitsumi PST3642UL (IC6023) pin 4. Used to monitor the state of +12V_MAIN power rail |

| B16 | CLK | OSCOUT | ? | Connected to crystal 32.768Khz |

| C1 | O | MK_I2C_SDA | ? | Connected to ICS1493G-18LFT clock generator (IC5001) pin 47 |

| C2 | PWR | AVREF2 | Ground | |

| C3 | N/A | N/A | N/A | Missing pad |

| C4 | N/A | N/A | N/A | Missing pad |

| C5 | N/A | N/A | N/A | Missing pad |

| C6 | N/A | N/A | N/A | Missing pad |

| C7 | N/A | N/A | N/A | Missing pad |

| C8 | N/A | N/A | N/A | Missing pad |

| C9 | N/A | N/A | N/A | Missing pad |

| C10 | N/A | N/A | N/A | Missing pad |

| C11 | N/A | N/A | N/A | Missing pad |

| C12 | N/A | N/A | N/A | Missing pad |

| C13 | N/A | N/A | N/A | Missing pad |

| C14 | N/A | N/A | N/A | Missing pad |

| C15 | PWR | VSSep | Ground | |

| C16 | CLK | OSCIN | ? | Connected to crystal 32.768Khz |

| D1 | O | MK_I2C_SCL | ? | Connected to ICS1493G-18LFT clock generator (IC5001) pin 46 |

| D2 | PWR | VDD2 | +1.5V_RSX_VDDIO | |

| D3 | N/A | N/A | N/A | Missing pad |

| D4 | O | XDR_FET_RST | Connected to XDRAM chips pin C15 (XDR_RQ_RST) | |

| D5 | O | XCG_EN | ? | Connected to ICS9218AGLFT (IC5002) pin 11 (switches BE_Y0_RQ_CTM/N, BE_Y1_RQ_CTM/N) Connected to ICS9218AGLFT (IC5003) pin 11 (switches BE_PLL_REFCLK_P/N) Connected to ICS9214DGLFT (IC5004) pin 11 (switches BE_RC_REFCLK_P/N, RSX_RC_REFCLK_P/N, SB_RC_REFCLK_P/N) |

| D6 | H | VD_CECI0 | Not Connected (CL4098) | |

| D7 | H | RSX_POW_FAIL | Connected to OnSemi NCP5318FTR2G (IC6201) pin 7 | |

| D8 | H | MUL_TRG_IN | ? | Connected to missing components (IC4003, IC4004, IC4005) pin 3 and 6 (related with BE_TRG_IN/OUT, RSX_TRG_IN/OUT, SB_TRG_IN/OUT) |

| D9 | H | SB_INT | ? | |

| D10 | F | MUL_TRG_OUT | ? | Connected to missing components (IC4006) pin 2 (related with BE_TRG_IN/OUT, RSX_TRG_IN/OUT, SB_TRG_IN/OUT) |

| D11 | F | SB_RESET | ? | Connected to 88SA8040-TBC1 SATA2PATA BluRay controller pin 17 Connected to GL852 (IC3305) USB HUB pin 38 Connected to Multi-card-board connector CN3219 pin 7 |

| D12 | F | PF2 BE_VCS_1.25_ON |

? | COK-001/COK-002 PF2 (Not connected) SEM-001 BE_VCS_1.25_ON |

| D13 | F | SW_1_A | ? | Connected to Mitsumi MM1593DFBEG (IC6020) pin 5 (switches +3.3V_MK_VDD) for Clock Synthesizer |

| D14 | N/A | N/A | N/A | Missing pad |

| D15 | CLK | 32KIN | ? | Connected to resistor 22ohm to pad D16 |

| D16 | CLK | 32KOUT | ? | Connected to resistor 1K to +3.3V_EVER |

| E1 | PWR | VSS | Ground | |

| E2 | N | RSX_SPI_CS | Connected to RSX pad AW8 (RSX SPI Bus) | |

| E3 | N/A | N/A | N/A | Missing pad |

| E4 | O | EJECT_MECHA | ? | Connected to BluRay Drive connector (CN3221) pin 56 |

| E5 | O | PO0 | Not Connected (CL4086) | |

| E6 | H | HDMI_INT | Connected to TC7WP3125FK (IC2501) pin 6 The TC7WP3125FK converts the signal originally triggered by Sil9132CBU pad E10 ? at 1.5V and converts it to 3.3V for syscon The TC7WP3125FK also converts the signal RS_SPDO0 (at 1.5V) into RS_SPDO0_33 (at 3.3V) | |

| E7 | H | MECHA_INT | ? | Not connected in retail PS3 models (testpad CL4102). The related SouthBridge pad is tied to GND with a 10k resistor (R3163) |

| E8 | H | MUL_CHKSTP_IN | ? | SB_CHKSTP_OUT |

| E9 | H | SYS_THR_ALRT | ? | Connected to CELL 90nm pad AP23 |

| E10 | F | MUL_CHKSTP_OUT | ? | |

| E11 | F | SB_CGRESET | ? | SB_CGRST (the name indicates that it resets the clock generator for the southbridge) |

| E12 | F | BT_WAKEON | Connected to wifi board connector (CN3701) pin 30 (BT_WAKE) | |

| E13 | F | PF1 BE_VCS_1.30_ON |

? | COK-001/COK-002 PF1 (Not connected) SEM-001 BE_VCS_1.30_ON |

| E14 | N/A | N/A | N/A | Missing pad |

| E15 | EEP | PP3 | ? | |

| E16 | EEP | SKB | ? | |

| F1 | N | RSX_SPI_DI | Connected to RSX pad BA7 (RSX SPI Bus) | |

| F2 | N | RSX_SPI_DO | Connected to RSX pad BA6 (RSX SPI Bus) | |

| F3 | N/A | N/A | N/A | Missing pad |

| F4 | O | HDMI_RST0 | ? | Connected to HDMI controller Sil9132CBU pad G2 ? |

| F5 | O | DISC_IN_MECHA | ? | Connected to BluRay Drive connector (CN3221) pin 55 |

| F6 | PWR | VDD3 | +3.3V_EVER | |

| F7 | PWR | AVDD | +3.3V_EVER | |

| F8 | PWR | VDD3 | +3.3V_EVER | |

| F9 | Not Connected | |||

| F10 | PWR | VDD3 | +3.3V_EVER | |

| F11 | PWR | VDDbat | Connected to CR2025 battery+ through two series diodes RB751S-40TE61 (D4008, D4007) | |

| F12 | D | MK_EN | ? | Connected to ICS1493G-18LFT clock generator (IC5001) pin 16 |

| F13 | D | SW_5_B | ? | Connected to Rohm BD3520FVM-TR (IC6200) pin 3 (switches +1.2V_RSX_VDDR) |

| F14 | N/A | N/A | N/A | Missing pad |

| F15 | EEP | PP0 | ? | |

| F16 | EEP | CSB | ? | |

| G1 | N | RSX_SPI_CLK | Connected to RSX pad AY8 (RSX SPI Bus) | |

| G2 | N | RSX_RESET | Connected to RSX pads AW5 (RESET) and AV6 (CGRESET) | |

| G3 | N/A | N/A | N/A | Missing pad |

| G4 | O | HDMI_RST1 | ? | Not connected ? (it seems to be a secondary reset signal for HDMI controller Sil9132CBU never used in retail PS3 models) |

| G5 | O | SW_AVCG PO5 |

? | Connected to ICS422AG-07LFT (IC2102) pin 12 (switches RSX_AVCLK0, RSX_AVCLK1, RSX_AVCLK2, RSX_AVCLK3) clocks for RSX and indirectly for EEGS<->RDRAM |

| G6 | PWR | AVSS | Ground | |

| G7 | PWR | VSS | Ground | |

| G8 | PWR | VSS | Ground | |

| G9 | Not Connected | |||

| G10 | PWR | VSS | Ground | |

| G11 | PWR | VDDep | +3.3V_EVER | |

| G12 | D | BEVRM_VID4 | ? | Connected to OnSemi NCP5318FTR2G (IC6103) pin 3 |

| G13 | D | BEVRM_VID5 | ? | Connected to OnSemi NCP5318FTR2G (IC6103) pin 30 |

| G14 | N/A | N/A | N/A | Missing pad |

| G15 | EEP | PP2 | ? | |

| G16 | EEP | DI | ? | |

| H1 | N | PN5 | Not Connected (CL4084) | |

| H2 | N | PN6 | Not Connected (CL4012) | |

| H3 | N/A | N/A | N/A | Missing pad |

| H4 | L | PL2 | Not Connected | |

| H5 | L | PL1 | Not Connected | |

| H6 | L | PL0 | Not Connected | |

| H7 | PWR | DVDD | +1.8V_EVER | |

| H08 | N/A | N/A | N/A | Missing pad |

| H09 | N/A | N/A | N/A | Missing pad |

| H10 | PWR | VDD3 | +3.3V_EVER | |

| H11 | CLK | TESTMODE | Not Connected | |

| H12 | D | BEVRM_VID2 | ? | Connected to OnSemi NCP5318FTR2G (IC6103) pin 1 |

| H13 | D | BEVRM_VID3 | ? | Connected to OnSemi NCP5318FTR2G (IC6103) pin 2 |

| H14 | N/A | N/A | N/A | Missing pad |

| H15 | EEP | PP1 | ? | |

| H16 | EEP | DO | ? | |

| J1 | N | RSX_FLDO1 | Connected to RSX pad AM40 | |

| J2 | N | RSX_INT | Connected to RSX pad AY7 | |

| J3 | N/A | N/A | N/A | Missing pad |

| J4 | L | PL4 | Not Connected | |

| J5 | L | PL3 | Not Connected | |

| J6 | PWR | VDD3 | +3.3V_EVER | |

| J7 | PWR | DVDD | +1.8V_EVER | |

| J08 | N/A | N/A | N/A | Missing pad |

| J09 | N/A | N/A | N/A | Missing pad |

| J10 | PWR | DVDD | +1.8V_EVER | |

| J11 | CLK | RST | ? | Connected to service connector (CN4009) pin 8 |

| J12 | D | BEVRM_VID0 | ? | Connected to OnSemi NCP5318FTR2G (IC6103) pin 31 |

| J13 | D | BEVRM_VID1 | ? | Connected to OnSemi NCP5318FTR2G (IC6103) pin 32 |

| J14 | N/A | N/A | N/A | Missing pad |

| J15 | EEP | WCB | ? | |

| J16 | EEP | RBB | ? | |

| K1 | N | VD_VINT0 | Connected to RSX pad AR22 (41x41 layout) | |

| K2 | N | VD_VINT1 | Connected to RSX pad AL38 (41x41 layout) | |

| K3 | N/A | N/A | N/A | Missing pad |

| K4 | L | PL6 | Not Connected | |

| K5 | L | PL5 | Not Connected | |

| K6 | PWR | VSSF | Ground | |

| K7 | JTAG | JTDI | ? | Connected to service connector (CN4009) pin 3 |

| K8 | JTAG | JTCK | ? | Connected to service connector (CN4009) pin 5 |

| K9 | JTAG | JTDO | ? | Connected to service connector (CN4009) pin 6 |

| K10 | PWR | DVDD | +1.8V_EVER | |

| K11 | PWR | VSSF | Ground | |

| K12 | C | I2CBUS_EN | ? | Connected to Toshiba TC7WB66FK pins 3 and 7 (IC5005 on SEM-001) through 1K resistor (in COK-001 the resistor is missing, a.k.a. this syscon line is N/C). This chip "duplicates" the MK_I2C_SCL/MK_I2C_SDA bus into a secondary XCG_I2C_SCL/XCG_I2C_SDA bus for the clock reference chip/s |

| K13 | C | PC7 | Not Connected (CL4085) | |

| K14 | N/A | N/A | N/A | Missing pad |

| K15 | EEP | PI6 | ? | |

| K16 | EEP | PI7 | ? | |

| L1 | PWR | VSS | Ground | |

| L2 | PWR | VDD0 | +1.2V_MC2_VDDIO | |

| L3 | N/A | N/A | N/A | Missing pad |

| L4 | L | PL8 | Not Connected | |

| L5 | L | PL7 | Not Connected | |

| L6 | PWR | VDDF | +3.3V_EVER | |

| L7 | JTAG | JNTRST | ? | Connected to service connector (CN4009) pin 2 ? |

| L8 | JTAG | JRTCK | ? | Connected to service connector (CN4009) pin 4 |

| L9 | JTAG | JTMS | ? | Connected to service connector (CN4009) pin 7 |

| L10 | PWR | DVDD | +1.8V_EVER | |

| L11 | PWR | DVDD | +1.8V_EVER | |

| L12 | C | RSXVRM_VID4 | Connected to OnSemi NCP5318FTR2G (IC6201) pin 3 | |

| L13 | C | RSXVRM_VID5 | Connected to OnSemi NCP5318FTR2G (IC6201) pin 30 | |

| L14 | N/A | N/A | N/A | Missing pad |

| L15 | I | DISC_CHUCK | ? | Connected to BluRay Drive connector (CN3221) pin 54 |

| L16 | I | SW_PCI | ? | Connected to Mitsumi MM1591FFBEG (IC6021) pin 5 (switches +1.5V_BRIDGE) for the PS2 bridge CXD9208GP Connected to Mitsumi MM1593DFBEG (IC6022) pin 5 (switches +3.3V_BRIDGE) for the PS2 bridge CXD9208GP Connected to PCI service connector pin 80 |

| M1 | M | BE_SPI_DI | ? | Connected to CELL 90nm pad AR13 (SPI Bus) |

| M2 | M | BE_SPI_CS | ? | Connected to CELL 90nm pad AP13 (SPI Bus) |

| M3 | N/A | N/A | N/A | Missing pad |

| M4 | A | PA0 | Not Connected (CL4092) | |

| M5 | A | WLAN_RESET | Connected to wifi board connector (CN3701) pin 29 (11G_RESET) | |

| M6 | A | PA4 | Not Connected (CL4087) | |

| M7 | A | POW_LED | ? | Connected to Switch board CSW-001 connector pin 6 |

| M8 | G | FANPWM1 | ? | Secondary fan output (non-retail PS3 models only) |

| M9 | G | BUZZER | Connected to Buzzer (BZ4001) through transistor DTC143ZUA-T106 (Q4014) | |

| M10 | G | XDR_FET_VREF | Connected to transistor DTC144EUA-T106 (Q4008). Switches XDR_RQ_VREF_FET | |

| M11 | G | SW_ATA | ? | Connected to UMH2NTN dual transistor (Q6009) pin 2 (switches +12V_BD) Connected to UMH2NTN dual transistor (Q6009) pin 5 (switches +5V_BD) Connected to UMH2NTN dual transistor (Q6006) pin 2 (switches +5V_HDD) |

| M12 | C | RSXVRM_VID2 | Connected to OnSemi NCP5318FTR2G (IC6201) pin 1 | |

| M13 | C | RSXVRM_VID3 | Connected to OnSemi NCP5318FTR2G (IC6201) pin 2 | |

| M14 | N/A | N/A | N/A | Missing pad |

| M15 | I | SW_2 | ? | Connected to Texas Instruments TPS51117PWRG4 (IC6302) pin 1 (switches +1.8V_VDD_MEM) |

| M16 | I | DISC_PHOT_LED | ? | Connected to BluRay Drive connector (CN3221) pin 53 |

| N1 | M | BE_SPI_CLK | ? | Connected to CELL 90nm pad AY13 (SPI Bus) |

| N2 | M | BE_SPI_DO | ? | Connected to CELL 90nm pad AV13 (SPI Bus) |

| N3 | N/A | N/A | N/A | Missing pad |

| N4 | A | SW_5_A | ? | Connected to OnSemi NCP5318FTR2G (IC6201) pin 29 Connected to Toshiba TC7SG08FU (IC6204) pin 1 Switches +1.2V_RSX_VDDC |

| N5 | A | BT_RESET | Connected to wifi board connector (CN3701) pin 10 (SYSCON_RST) | |

| N6 | A | AUDIO_MUTE | ? | Connected to transistor DTA144EUA-T106 (Q2404). Switches Cirrus CX4351-CZZR pin 18 (AOUTA) left audio channel and pin 15 (AOUTB) right audio channel, that are connected to MultiAV connector pin 11 (AUL) and pin9 (AUR) respectivelly |

| N7 | A | STBY_LED | ? | Connected to Switch board CSW-001 connector pin 7 |

| N8 | G | FANPWM0 | ? | Primary fan output (all PS3 models) |

| N9 | G | SW_PWM | ? | Connected to Switch board CSW-001 connector pin 2 |

| N10 | G | XDR_FET_SCK | Connected to transistor SST222AT116 (Q1302) BE_RQ_SCK_BJT | |

| N11 | G | SW_4_A | Connected to wifi board connector (CN3701) pin 9 (11G_PWR_EN) Connected to base pin of transistor UMH2NTN (Q3501) who switches IC3502 pin 5, and IC3501 pin 3 (+1.2V_ESW, +1.9V_ESW, +3.3V_ESW for Ethernet Controller) | |

| N12 | C | RSXVRM_VID0 | Connected to OnSemi NCP5318FTR2G (IC6201) pin 31 | |

| N13 | C | RSXVRM_VID1 | Connected to OnSemi NCP5318FTR2G (IC6201) pin 32 | |

| N14 | N/A | N/A | N/A | Missing pad |

| N15 | I | BACKUP_MODE | ? | Connected to service connector (CN4009) pin 14 |

| N16 | I | DIAG_MODE | ? | Connected to service connector (CN4009) pin 13 |

| P1 | M | BE_POWGOOD | ? | Connected to CELL 90nm pad AV20 |

| P2 | M | BE_RESET | ? | Connected to CELL 90nm pad AW20 |

| P3 | N/A | N/A | N/A | Missing pad |

| P4 | N/A | N/A | N/A | Missing pad |

| P5 | N/A | N/A | N/A | Missing pad |

| P6 | N/A | N/A | N/A | Missing pad |

| P7 | N/A | N/A | N/A | Missing pad |

| P8 | N/A | N/A | N/A | Missing pad |

| P9 | N/A | N/A | N/A | Missing pad |

| P10 | N/A | N/A | N/A | Missing pad |

| P11 | N/A | N/A | N/A | Missing pad |

| P12 | N/A | N/A | N/A | Missing pad |

| P13 | N/A | N/A | N/A | Missing pad |

| P14 | N/A | N/A | N/A | Missing pad |

| P15 | P | UART0_RxD | ? | Connected to service connector (CN4009) pin 10 (Serial Receive) |

| P16 | P | UART0_TxD | ? | Connected to service connector (CN4009) pin 11 (Serial Transmit) |

| R1 | M | PM7 | Not Connected (CL4011) | |

| R2 | M | PM6 | Not Connected (CL4010) | |

| R3 | PWR | VDD1 | +1.2V_MC2_VDDIO | |

| R4 | PWR | AVSUO | Ground | |

| R5 | PWR | AVDUO | +3.3V_EVER | |

| R6 | PWR | VSS | Ground | |

| R7 | PWR | DVDD | +1.8V_EVER | |

| R8 | Q | RSX_FBVDD_SEL | Connected to Texas Instruments SN105233DBTR (IC6301) through transistor/s | |

| R9 | Q | PQ1 | Not Connected (CL4020) | |

| R10 | Q | RMC_IN | ? | Connected to Switch board CSW-001 connector pin 3 Connected to service connector (CN4009) pin 17 |

| R11 | B | VD_CECO0 | Not Connected (CL4100) | |

| R12 | B | SW_3 | ? | Connected to Rohm BD3520FVM-TR (IC6305) pin 3 (switches +1.2V_SB_VDDC and +1.2V_SB_VDDR) |

| R13 | B | SW_1_B | ? | Connected to Mitsumi MM1562ZFBE (IC6013) pin 5 (switches +2.5V_LREG_XCG_500_MEM) Connected to Toshiba TC7WB66FK (IC5005) pins 3 and 7, and to (IC5006) pin 4, through 1K resistor. The TC7WB66FK chip "duplicates" the MK_I2C_SCL/MK_I2C_SDA bus into a secondary XCG_I2C_SCL/XCG_I2C_SDA bus for the clock reference chip/s Analog Voltage for the core PLL of IC5004, Clock Generator used to support the Rambus XDR memory subsystem and Redwood logic interface. |

| R14 | B | SW_7_A | ? | Connected to OnSemi NCP5318FTR2G (IC6103) pin 29 Connected to Toshiba TC7SG08FU (IC6107) pin 1 Switches +1.0V_BE_VDDC Cell BE core voltage supply (VDD) then VCS (the core array voltage). Note, the VID values stored on the CELL itself are not available to be read yet. So the default VID of the VRM is used until then. |

| R15 | P | HDMI_I2C_SDA | ? | Connected to HDMI controller Sil9132CBU pad D2 |

| R16 | P | HDMI_I2C_SCL | ? | Connected to HDMI controller Sil9132CBU pad E2 |

| T1 | Not Connected | |||

| T2 | M | BE_INT | ? | Connected to CELL 90nm pad AW19 |

| T3 | PWR | VSS | Ground | |

| T4 | CLK | XTAL | ? | Connected to crystal 16.9344Mhz |

| T5 | CLK | EXTAL | ? | Connected to crystal 16.9344Mhz |

| T6 | PWR | VSS | Ground | |

| T7 | CLK | XXTALO | Not Connected (CL4040) | |

| T8 | Q | THR_I2C_SCL | Connected to Thermal#Temperature_Monitors | |

| T9 | Q | THR_I2C_SDA | Connected to Thermal#Temperature_Monitors | |

| T10 | Q | PQ4 | Not Connected (CL4021) | |

| T11 | Q | PQ5 | Not Connected (CL4022) | |

| T12 | B | VD_CECO1 | Not Connected (CL4101) | |

| T13 | B | SW_4_B | ? | Connected to 88E6108 ethernet controller (IC3503) pin 94 (signal named P3_ENABLE_PD) Connected to (Q6003) transistor (switches +3.3V_SB_VDDIO) Connected to OnSemi NCP511SN25T1G (IC6011) pin 3 (switches +2.5V_SB_PLL_VDDC) Connected to Mitsumi MM1591JFBEG (IC6014) pin 5 (switches +1.8V_SB_PERI) Connected to UMH2NTN dual transistor (Q6006) pin 5 (switches +5V_USB) |

| T14 | B | SW_6 | ? | Connected to Rohm BD3520FVM-TR (IC6303) pin 3 (switches +1.2V_YC_RC_VDDIO) Connected to Mitsumi MM3141CNRE (IC6012) pin 3 (switches +1.2V_MC2_VDDIO) I/O voltage supplies, VDD_IO for CELL, RSX and South Bridge |

| T15 | B | SW_8_A | ? | Connected to Rohm BD3504FVM-TR (IC6304) pin 3 (switches +1.5V_YC_RC_VDDA) Connected to Texas Instruments TPS73101DBVRG4 (IC6007) pin 3 (switches +1.6V_BE_VDDA) |

| T16 | Not Connected | |||