Timebases: Difference between revisions

m (→References) |

m (→References) |

||

| Line 241: | Line 241: | ||

See also: | See also: | ||

* [http://www.ps3devwiki.com/files/documents | * [http://www.ps3devwiki.com/files/documents/BE_Hardwar_Init_Guide_v1.3_31March2006.pdf BE_Hardwar_Init_Guide_v1.3_31March2006.pdf] // (mirror: [http://www.capsl.udel.edu/~jmanzano/Cell/docs/arch/BE_Hardwar_Init_Guide_v1.3_31March2006.pdf BE_Hardwar_Init_Guide_v1.3_31March2006.pdf]) - esp. pages 21-22 | ||

* [http://www.ps3devwiki.com/files/documents/Cell%20BE/CellBE_HIG_90nm_v1.5_30Nov2007_pub.pdf CellBE_HIG_90nm_v1.5_30Nov2007_pub.pdf] // (mirror: [https://www-01.ibm.com/chips/techlib/techlib.nsf/techdocs/BD3F1F4C3DB32C7487257142006131BC/$file/CellBE_HIG_90nm_v1.5_30Nov2007_pub.pdf CellBE_HIG_90nm_v1.5_30Nov2007_pub.pdf]) - esp. pages 26-27 | * [http://www.ps3devwiki.com/files/documents/-Cell%20BE/CellBE_HIG_90nm_v1.5_30Nov2007_pub.pdf CellBE_HIG_90nm_v1.5_30Nov2007_pub.pdf] // (mirror: [https://www-01.ibm.com/chips/techlib/techlib.nsf/techdocs/BD3F1F4C3DB32C7487257142006131BC/$file/CellBE_HIG_90nm_v1.5_30Nov2007_pub.pdf CellBE_HIG_90nm_v1.5_30Nov2007_pub.pdf]) - esp. pages 26-27 | ||

* [http://www.ps3devwiki.com/files/documents/-Cell%20BE/CellBE_HIG_65nm_v1.01_8Jun2007.pdf CellBE_HIG_65nm_v1.01_8Jun2007.pdf] // (mirror: [https://www-01.ibm.com/chips/techlib/techlib.nsf/techdocs/AF7832F379790768872572D10047E52B/$file/CellBE_HIG_65nm_v1.01_8Jun2007.pdf CellBE_HIG_65nm_v1.01_8Jun2007.pdf]) - esp. pages 25-26 | * [http://www.ps3devwiki.com/files/documents/-Cell%20BE/CellBE_HIG_65nm_v1.01_8Jun2007.pdf CellBE_HIG_65nm_v1.01_8Jun2007.pdf] // (mirror: [https://www-01.ibm.com/chips/techlib/techlib.nsf/techdocs/AF7832F379790768872572D10047E52B/$file/CellBE_HIG_65nm_v1.01_8Jun2007.pdf CellBE_HIG_65nm_v1.01_8Jun2007.pdf]) - esp. pages 25-26 | ||

* [http://www.ps3devwiki.com/files/documents/-Cell%20BE/Cell%20Broadband%20Engine%20processor%20Design%20and%20implementation%20-%20M.W.%20Rriley%20-%20J.D.%20Warnock%20-%20D.F.%20Wendel.pdf Cell Broadband Engine processor Design and implementation - M.W. Rriley - J.D. Warnock - D.F. Wendel.pdf] - esp. pages 5-6 | * [http://www.ps3devwiki.com/files/documents/-Cell%20BE/Cell%20Broadband%20Engine%20processor%20Design%20and%20implementation%20-%20M.W.%20Rriley%20-%20J.D.%20Warnock%20-%20D.F.%20Wendel.pdf Cell Broadband Engine processor Design and implementation - M.W. Rriley - J.D. Warnock - D.F. Wendel.pdf] - esp. pages 5-6 | ||

Revision as of 15:23, 19 June 2012

IC Clockgen

ICS ICS1493G-18LFT

6-710-156-01 / IC5001

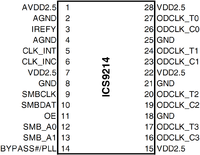

ICS ICS9218AGLFT (IC CLOCK GEN RAMBUS XDR 28-TSSOP)

6-710-157-01 / IC5002, IC5003 See: RAM

ICS ICS9214DGLFT (IC CLOCK GEN RAMBUS XDR 28-TSSOP)

| Pin | Signal | Description |

|---|---|---|

| 1 | AVDD2.5 | |

| 2 | AGND | |

| 3 | IREFY | |

| 4 | AGND | |

| 5 | CLK_INIT | |

| 6 | CLK_INC | |

| 7 | VDD2.5 | |

| 8 | GND | |

| 9 | SMBCLK | |

| 10 | SMBDAT | |

| 11 | OE | |

| 12 | SMB_A0 | |

| 13 | SMB_01 | |

| 14 | BYPASS#/PLL | |

| 15 | VDD2.5 | |

| 16 | 0DCLK_C3 | |

| 17 | 0DCLK_T3 | |

| 18 | GND | |

| 19 | 0DCLK_C2 | |

| 20 | 0DCLK_T2 | |

| 21 | GND | |

| 22 | VDD2.5 | |

| 23 | 0DCLK_C1 | |

| 24 | 0DCLK_T1 | |

| 25 | GND | |

| 26 | 0DCLK_C0 | |

| 27 | 0DCLK_T0 | |

| 28 | VDD2.5 |

6-710-154-01 / IC5004

Datasheet: ICS9214DGLFT.pdf (224.57 KB)

See: RAM

ICS ICS422AG-07LFT (IC CLOCK GEN RSX AV_CLK 24-TSSOP)

ICS ICS422AG-07LFT

6-710-158-01 / IC2102

http://www.ps3devwiki.com/index.php?title=File:ICS_422AG07LF.JPG

Used for RSX AV_CLK

See: RSX

| Pin | Signal | Description |

|---|---|---|

| 1 | XIN | from X2101 24.576MHz |

| 2 | VDD | +3.3V_ANA via FB2101 0 uH |

| 3 | GND | Ground |

| 4 | 54M | to RSX_AVCLK0 via R2103 43.2 Ohm |

| 5 | GND | Ground |

| 6 | VDD54 | +1.5_AVCG_VDDIO via FB2102 0 uH |

| 7 | VDD | +3.3V_ANA via FB2101 0 uH |

| 8 | GND | Ground |

| 9 | 53.946M | to RSX_AVCLK1 via R2104 43.2 Ohm |

| 10 | GND | Ground |

| 11 | VDD53 | +1.5_AVCG_VDDIO via FB2102 0 uH |

| 12 | OE | from SW_AVCG |

| 13 | SEL | from RSX_GPIO0 |

| 14 | VDDAUD | +1.5_AVCG_VDDIO via FB2102 0 uH |

| 15 | GND | Ground |

| 16 | AUDIO | to pin2 IC2105 via R2117 / to RSX_AVCLK3 via R2109 39 Ohm |

| 17 | GND | Ground |

| 18 | VDD | +3.3V_ANA via FB2101 0 uH |

| 19 | VDD | +3.3V_ANA via FB2101 0 uH |

| 20 | GND | Ground |

| 21 | 24.576M | to RSX_AVCLK2 via R2108 43.2 Ohm |

| 22 | GND | Ground |

| 23 | VDDREF | +1.5_AVCG_VDDIO via FB2102 0 uH |

| 24 | XOUT | to X2101 24.576MHz via R2107 0 Ohm |

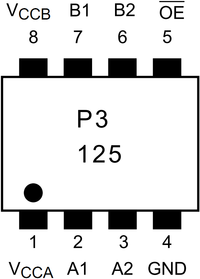

Toshiba TC7WP3125FK(T5RSOF (2bit Dual Supply Bus Buffer RSX Audio)

Toshiba TC7WP3125FK(T5RSOF

6-710-429-01 / IC2105, IC2501

Datasheet: TC7WP3125FC_TC7WP3125FK_en_datasheet_080602.pdf

http://www.ps3devwiki.com/index.php?title=File:TC7WP3125FK.png

Used for RSX Audio

| Pin | Signal | Description |

|---|---|---|

| 1 | VCCA | +1.5V_AVCG_VDDIO |

| 2 | A1 | from pin16 (audio) of IC2102 (ICS ICS422AG-07LFT) via R2117 43.2 Ohm |

| 3 | A2 | to Ground |

| 4 | GND | Ground |

| 5 | /OE | to PCLKEN via buffer Q2101 (DTC144EUA-T106) / R2180 10K Ohm |

| 6 | B2 | - |

| 7 | B1 | to DRCG_GEN18M via R2123 33 Ohm |

| 8 | VCCB | from 1.8V_EEGS_VDDIO via R2122 0 Ohm |

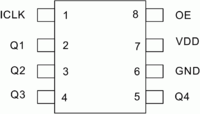

ICS ICS651MLFT (Low Skew 1 To 4 Clock Buffer RSX Audio SOIC8P)

ICS ICS651MLFT

6-710-430-01 / IC2108

Datasheet: ICS651MLFT.pdf (185.76 KB)

http://www.ps3devwiki.com/index.php?title=File:ICS651MLFT-SOIC8P.png

Used for RSX Audio

| Pin | Signal | Description |

|---|---|---|

| 1 | ICLK | from RS_MCLKO0 |

| 2 | Q1 | to HDMI_MCLKO0 via R2177 33 Ohm |

| 3 | Q2 | - |

| 4 | Q3 | to ADAC_MCLKO0 via R2179 33 Ohm |

| 5 | Q4 | - |

| 6 | GND | Ground |

| 7 | VDD | +1.5V_RSX_VDDIO |

| 8 | OE | to +1.5V_RSX_VDDIO |

Crystals

Crystal : 24.576MHz

COK-001/COK-002/SEM-001

1-813-876-11 / X2101

Used for IC2102 : RSX_AVCLK

See: RSX

Crystal : 18.432MHz

COK-002

1-795-980-21 / X2200

Crystal : 12MHz

COK-001/COK-002/SEM-001

1-813-877-11 / X3301

Crystal : 25MHz

COK-001/COK-002

1-813-052-21 / X3402

SEM-001

1-813-052-21 / X3401

Crystal : 25MHz

COK-001/COK-002/SEM-001

1-813-052-21 / X3501

Crystal : 16.9344MHz

COK-001/COK-002/SEM-01

1-781-768-21 / X4001

Crystal : 32.768kHz

COK-001/COK-002/SEM-001

1-781-786-21 / X4002

Crystal : 14.31818MHz

COK-001/COK-002/SEM-001

1-813-875-11 / X5001

References

See also:

- BE_Hardwar_Init_Guide_v1.3_31March2006.pdf // (mirror: BE_Hardwar_Init_Guide_v1.3_31March2006.pdf) - esp. pages 21-22

- CellBE_HIG_90nm_v1.5_30Nov2007_pub.pdf // (mirror: CellBE_HIG_90nm_v1.5_30Nov2007_pub.pdf) - esp. pages 26-27

- CellBE_HIG_65nm_v1.01_8Jun2007.pdf // (mirror: CellBE_HIG_65nm_v1.01_8Jun2007.pdf) - esp. pages 25-26

- Cell Broadband Engine processor Design and implementation - M.W. Rriley - J.D. Warnock - D.F. Wendel.pdf - esp. pages 5-6