K4Y50164UE-JCB3: Difference between revisions

Jump to navigation

Jump to search

mNo edit summary |

m (specs replaced by a template) |

||

| (One intermediate revision by one other user not shown) | |||

| Line 2: | Line 2: | ||

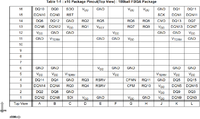

<div style="float:right">[[File:K4Y50164UE-JCB3.png|200px|thumb|left|100-ball FBGA<br />Samsung K4Y50164UE-JCB3]]</div> | <div style="float:right">[[File:K4Y50164UE-JCB3.png|200px|thumb|left|100-ball FBGA<br />Samsung K4Y50164UE-JCB3]]</div> | ||

([[CECHGxx]]/[[SEM-00x|SEM-001]], [[CECHJxx]]/[[DIA-00x#DIA-002|DIA-002]], [[CECHKxx]]/[[DIA-00x#DIA-002|DIA-002]]) | ([[CECHGxx]]/[[SEM-00x|SEM-001]], [[CECHJxx]]/[[DIA-00x#DIA-002|DIA-002]], [[CECHKxx]]/[[DIA-00x#DIA-002|DIA-002]], [[CECH-20xx]]/[[DYN-001]]) | ||

Datasheet: [http://www.samsung.com/global/system/business/semiconductor/product/2007/6/11/XDR_RDRAM/XDRDRAM/Component/512Mbit/K4Y50164UE/ds_k4y50xx4ue_rev10.pdf Samsung K4Y50164UE-JCB3] | Datasheet: [http://www.samsung.com/global/system/business/semiconductor/product/2007/6/11/XDR_RDRAM/XDRDRAM/Component/512Mbit/K4Y50164UE/ds_k4y50xx4ue_rev10.pdf Samsung K4Y50164UE-JCB3] | ||

{{Samsung memory product code}} | |||

{{Wikify}} | {{Wikify}} | ||

Latest revision as of 09:45, 14 April 2021

Samsung K4Y50164UE-JCB3[edit | edit source]

(CECHGxx/SEM-001, CECHJxx/DIA-002, CECHKxx/DIA-002, CECH-20xx/DYN-001)

Datasheet: Samsung K4Y50164UE-JCB3

| Manufacturer | DRAM | DRAM type | Density | Organization | Banks | Interface | Revision | Package type | Power & Temp. | Speed |

|---|---|---|---|---|---|---|---|---|---|---|

| K: Samsung | 4: DRAM | J: GDDR3 SDRAM Y: XDR DRAM G: GDDR5 SDRAM |

10: 1G, 8K/32ms 50: 512M, 32K/16ms 52: 512M, 8K/32ms 12: ? |

16: x16bit 32: x32bit |

4: 8 Banks 5: 16 Banks |

U: DRSL, 1.8V, 1.2V Q: SSTL-2 1.8V, 1.8V K: ? T: ? F: POD_15(1.5V,1.5V) |

C: 4th Gen. E: 6th Gen. G: 8th Gen. I: 10th Gen. J: 11th Gen. |

J: BOC (Lead-free) S: ? K: ? H (GDDR5): FBGA-170 |

C: Normal Power (0ºC–95ºC) | B3 (XDR): 3.2Gbps, 35ns, 20Cycles 14 (GDDR3): 1.4ns (700MHz) 15 (GDDR5): 1.5ns (667MHz) |

| This article is marked for rewrite/restructuring in proper wiki format. You can help PS3 Developer wiki by editing it. |

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||