|

|

| Line 51: |

Line 51: |

| Unknown bridge chip from EE+GS to the CXM4024R (see [[MultiAV]]) and the [[RSX]] <br /> | | Unknown bridge chip from EE+GS to the CXM4024R (see [[MultiAV]]) and the [[RSX]] <br /> |

| http://www.ps3devwiki.com/index.php?title=File:SCEI_CXD9208GP.JPG <br /> | | http://www.ps3devwiki.com/index.php?title=File:SCEI_CXD9208GP.JPG <br /> |

|

| |

| == PS2 Software ==

| |

| [[Category:Software]]

| |

|

| |

| Mountpoints:

| |

| * dev_ps2disc

| |

| * dev_ps2disc1

| |

|

| |

| {| border="1" cellspacing="0" cellpadding="5" border="#999" class="wikitable" style="border:1px solid #999; border-collapse: collapse;"

| |

| |- bgcolor="#cccccc"

| |

| ! Name !! Auth ID !! Self<br />(/dev_flash/ps2emu) !! Notes

| |

| |-

| |

| | PS2_LPAR || 0x1020000003000001 || rowspan="2" | ps2_emu.self ||

| |

| |-

| |

| | *SCE_CELLOS_SYSTEM_MGR_PS2 || 0x107000001D000001 ||

| |

| |-

| |

| | PS2_GX_LPAR || 0x1020000003000001 || rowspan="2" | ps2_gxemu.self ||

| |

| |-

| |

| | *SCE_CELLOS_SYSTEM_MGR_PS2_GX || 0x107000001D000001 ||

| |

| |-

| |

| | PS2_SW_LPAR || 0x1020000003000001 || rowspan="2" | ps2_softemu.self ||

| |

| |-

| |

| | *SCE_CELLOS_SYSTEM_MGR_PS2_SW || 0x107000001D000001 ||

| |

| |-

| |

| |}

| |

|

| |

| {| border="1" cellspacing="0" cellpadding="5" border="#999" class="wikitable" style="border:1px solid #999; border-collapse: collapse;"

| |

| |- bgcolor="#cccccc"

| |

| ! colspan="4" | PS2_GX

| |

| |-

| |

| ! Core !! Job !! Source !! Notes

| |

| |-

| |

| | SPU0 || IOP || SPU ASM ||

| |

| |-

| |

| | SPU1 || DMA || SPU ASM ||

| |

| |-

| |

| | SPU2 || Isolation || C++ Raw SPU || Used for MagicGate Encryption and others (?)

| |

| |-

| |

| | SPU3 || IPU || SPU ASM ||

| |

| |-

| |

| | SPU4 || GFIF || SPU ASM ||

| |

| |-

| |

| | SPU5 || PS2-SPU2 || C++ || about 50% load average

| |

| |-

| |

| | SPU6 || VU1 || SPU ASM ||

| |

| |-

| |

| | SPU7 || - || - || Unavailable: Factory disabled SPU

| |

| |-

| |

| | PPU:0 || PS2-Devices || C++ and PPU ASM ||

| |

| |-

| |

| | PPU:1 || Emotion Engine || C++ and PPU ASM ||

| |

| |-

| |

| | PS2-GS || Graphic Synthesizer || Hardware PS2-GS || Present in CECHC/COK-002

| |

| |-

| |

| ! colspan="4" | PS2 (GS+EE)

| |

| |-

| |

| ! Core !! Job !! Source !! Notes

| |

| |-

| |

| | SPU0 || IOP || SPU ASM ||

| |

| |-

| |

| | SPU2 || Isolation || C++ Raw SPU || Used for MagicGate Encryption and others (?)

| |

| |-

| |

| | - || DMA || Hardware PS2-EE ||

| |

| |-

| |

| | - || VU1 || Hardware PS2-EE ||

| |

| |-

| |

| | - || IPU || Hardware PS2-EE ||

| |

| |-

| |

| | - || GFIF || Hardware PS2-EE ||

| |

| |-

| |

| | SPU5 || PS2-SPU2 || C++ || about 50% load average

| |

| |-

| |

| | SPU7 || - || - || Unavailable: Factory disabled SPU

| |

| |-

| |

| | PPU:0 || PS2-Devices || C++ and PPU ASM ||

| |

| |-

| |

| | PPU:1 || - || - || unused?

| |

| |-

| |

| | PS2-EE || Emotion Engine || Hardware PS2-EE || Present in CECHA/COK-001 and CECHB/COK-001

| |

| |-

| |

| | PS2-GS || Graphic Synthesizer || Hardware PS2-GS || Present in CECHA/COK-001 and CECHB/COK-001

| |

| |-

| |

| ! colspan="4" | PS2 Software

| |

| |-

| |

| | colspan="5" | problematic, see Mathieulh quoted below

| |

| <pre>

| |

| The main issue here is that it's mostly not doable to emulate the GS efficiently with the rest

| |

| of the hardware because the RSX is just not meant for this task and cannot emulate the GS on

| |

| its own while all the available SPUs and the PPU are already mostly fully used to emulate the

| |

| rest of the playstation 2 hardware, this explains why sony never could finish the ps2_softemu

| |

| and that it reached a stalling step.

| |

|

| |

| I honestly have no idea on how it would be possible to get over the ps3 hardware limitations to

| |

| perform a full ps2 emulation without any of the ps2 hardware present on the console, one thing

| |

| for sure is that the emulator would have to be entirely rewritten and optimized like no other

| |

| ps3 software has been.

| |

| </pre>

| |

| |-

| |

| |}

| |

PS2-Compatibility

Early PS3 FAT CECHA/COK-001 and CECHB/COK-001 : Full compatibility with GS+EE and Rambus memory. Later CECHC/COK-002 had instead of GS+EE a single GS and lacked the Rambus memory.

PS2 Hardware

PS2 EE/GS and PS2 GS

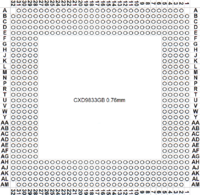

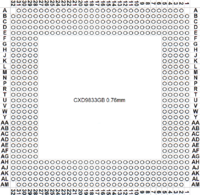

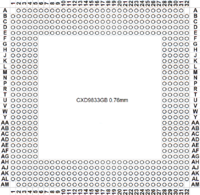

IC7004, (PS2 EE/GS)

Productcode: Sony CXD9833GB

PartNo.: 8-753-227-14

BALL-GRID-ARRAY overview CPU view

facing BGA A1 marker:northeast/topright

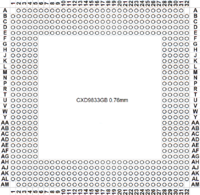

IC7004, (PS2 EE/GS)

Productcode: Sony CXD9833GB

PartNo.: 8-753-227-14

BALL-GRID-ARRAY overview PCB view

facing BGA A1 marker:northwest/topleft

Sony CXD2953AGB (PS2 EE/GS)

Used on PS3 FAT CECHA/COK-001 and CECHB/COK-001

http://www.ps3devwiki.com/index.php?title=File:SCEI_CXD2953AGB.JPG

Sony CXD9833GB (PS2 EE/GS)

8-753-227-14 / IC7004

http://www.ps3devwiki.com/index.php?title=File:CXD9833GB.png

BGA 536 (32x32 minus 22*22 center square minus 4 cornerpads)

pitch : 0.76mm

Sony CXD2972GB (PS2 GS)

Used on PS3 FAT CECHC/COK-002

http://www.ps3devwiki.com/index.php?title=File:CXD2972GB.JPG

PS2 Rambus 32MB memory

54-ball FBGA

Samsung K4R271669F / K4R271669H

Rambus

The earlier models with hardware PS2 compatibility also contained an extra 32MB of RDRAM using two 16MB Samsung chips.

| Type |

Size |

Speed |

Voltage |

Packaging |

Manufacturer |

Serial Number |

Description

|

| RDRAM |

16MB |

800MHz |

2.50 +/- 0.13V |

54-pin |

Samsung |

K4R271669F |

32MB total (2 chips) PS2 HW BC

|

| RDRAM |

16MB |

800MHz |

2.50 +/- 0.13V |

54-pin |

Samsung |

K4R271669H |

32MB total (2 chips) PS2 HW BC

|

Samsung K4R271669F / K4R271669H (PS2 Rambus 800MHz 16MB 2.5V FBGA54 - 2x)

Used on PS3 FAT CECHA/COK-001 and CECHB/COK-001

Datasheet: ds_k4r271669h_rev10.pdf

http://www.ps3devwiki.com/index.php?title=File:K4R271669F.png

PS2 bridgechip

Sony CXD9208GP2 (PS2 ?)

6-710-433-01 / IC7301

Used on PS3 FAT CECHA/COK-001 and CECHB/COK-001

Unknown bridge chip from EE+GS to the CXM4024R (see MultiAV) and the RSX

http://www.ps3devwiki.com/index.php?title=File:SCEI_CXD9208GP.JPG