Hardware Flashers:testpoints layout 2

Jump to navigation

Jump to search

NOR Consoles[edit | edit source]

Used in the last revisions of the fatter model PS3 (CECHL, CECHM, CECHP, CECHQ)

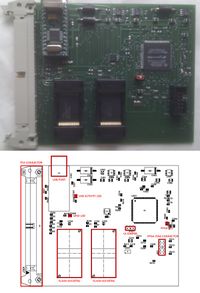

NOR Wiring - layout 2[edit | edit source]

Flashers for NOR based consoles (CECHH/DIA-001 and later) are generaly wired to the testpoints between South Bridge and NOR), plus (when needed) ground and Vcc.

CECHL/VER-001, CECHM/VER-001, CECHP/VER-001, CECHQ/VER-001 all have same layout 2 of testpoints.

TriState on NOR consoles[edit | edit source]

NOR Pinout table[edit | edit source]

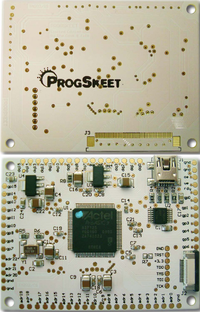

| NORpin | PAD | Progskeet 1.0 / 1.1 | Progskeet 1.2 | Teensy++ 2.0 NORway |

PNM | E3 / E3 Linker | NOR56 360clip | Remark |

|---|---|---|---|---|---|---|---|---|

| 31 | A0 | adr0 | P11 | F0 | A0 | A0 | FA0 | |

| 26 | A1 | adr1 | P12 | F1 | A1 | A1 | FA1 | |

| 25 | A2 | adr2 | P13 | F2 | A2 | A2 | FA2 | |

| 24 | A3 | adr3 | P14 | F3 | A3 | A3 | FA3 | |

| 23 | A4 | adr4 | P15 | F4 | A4 | A4 | FA4 | |

| 22 | A5 | adr5 | P16 | F5 | A5 | A5 | FA5 | |

| 21 | A6 | adr6 | P17 | F6 | A6 | A6 | FA6 | |

| 20 | A7 | adr7 | P18 | F7 | A7 | A7 | FA7 | |

| 10 | A8 | adr8 | P19 | PA0 | A8 | A8 | FA8 | |

| 9 | A9 | adr9 | P20 | PA1 | A9 | A9 | FA9 | |

| 8 | A10 | adr10 | P21 | PA2 | A10 | A10 | FA10 | |

| 7 | A11 | adr11 | P22 | PA3 | A11 | A11 | FA11 | |

| 6 | A12 | adr12 | P23 | PA4 | A12 | A12 | FA12 | |

| 5 | A13 | adr13 | P24 | PA5 | A13 | A13 | FA13 | |

| 4 | A14 | adr14 | P25 | PA6 | A14 | A14 | FA14 | |

| 3 | A15 | adr15 | P26 | PA7 | A15 | A15 | FA15 | |

| 54 | A16 | adr16 | P27 | B0 | A16 | A16 | FA16 | |

| 19 | A17 | adr17 | P28 | B1 | A17 | A17 | FA17 | |

| 18 | A18 | adr18 | P29 | B2 | A18 | A18 | FA18 | |

| 11 | A19 | adr19 | P30 | B3 | A19 | A19 | FA19 | |

| 12 | A20 | adr20 | P31 | B4 | A20 | A20 | FA20 | |

| 15 | A21 | adr21 | P32 | B5 | A21 | A21 | FA21 | |

| 1 | A23 | Not Used | Not Used | Not Used | Not Used | Not Used | FA23 | pin unused for 128mbit and below |

| 56 | A24 | Not Used | Not Used | Not Used | Not Used | Not Used | FA24 | pin unused for 256mbit and below |

| 2 | A22 | adr22 | P33 | B6 | A22 | A22 | FA22 | |

| 35 | DQ0 | dq0 | P34 | D0 | DQ0 | D0 | AD0 | |

| 37 | DQ1 | dq1 | P35 | D1 | DQ1 | D1 | AD1 | |

| 39 | DQ2 | dq2 | P36 | D2 | DQ2 | D2 | AD2 | |

| 41 | DQ3 | dq3 | P37 | D3 | DQ3 | D3 | AD3 | |

| 44 | DQ4 | dq4 | P38 | D4 | DQ4 | D4 | AD4 | |

| 46 | DQ5 | dq5 | P39 | D5 | DQ5 | D5 | AD5 | |

| 48 | DQ6 | dq6 | P40 | D6 | DQ6 | D6 | AD6 | |

| 50 | DQ7 | dq7 | P41 | D7 | DQ7 | D7 | AD7 | |

| 36 | DQ8 | dq8 | P42 | C0 | DQ8 | D8 | AD8 | |

| 38 | DQ9 | dq9 | P43 | C1 | DQ9 | D9 | AD9 | |

| 40 | DQ10 | dq10 | P44 | C2 | DQ10 | D10 | AD10 | |

| 42 | DQ11 | dq11 | P45 | C3 | DQ11 | D11 | AD11 | |

| 45 | DQ12 | dq12 | P46 | C4 | DQ12 | D12 | AD12 | |

| 47 | DQ13 | dq13 | P47 | C5 | DQ13 | D13 | AD13 | |

| 49 | DQ14 | dq14 | P48 | C6 | DQ14 | D14 | AD14 | |

| 51 | DQ15 | dq15 | P49 | C7 | DQ15 | D15 | AD15 | |

| 13 | #WE | we | P09 | E5 | NWE | NWE | WE | |

| 32 | CE# | gp0 | P07(p) CE_A / P02(s) CE_B | E0 | NCE | CE to NOR (SBCE from South Bridge) |

CE# | |

| 14 | RESET | gp1 | P06 | E4 | NRESET | RESET | RESET | |

| N/A | TRISTATE | gp2 | P05 | E7 | GPIO0 | SBE | N/A | |

| 16 | WP# | gp3 | P04 | Not Used | NWPACC | Not used | WP# | Is tied to Vcc by mobo |

| 53 | BYTE# | Not Used | Not used | Not used | Not used | BVCC | ? | Is tied to Vcc by mobo |

| 34 | OE# | oe | P10 | E1 | NOE | NOE | OE | |

| 17 | RY/BY# | rdy (ánd gp4 for old bitstream) | P08 | E6 | RYNBY | NWAIT | RDY | JTAG updated progskeet can do without the progskeet:gp4 to progskeet:rdy bridge and use the PS3:RY/BY# to progskeet:rdy alone. |

| 33, 52 | VSS | GND | GND | GND | GND | GND | ||

| 29, 43 | VCC | Not Used | Not used | Not used | VCC | ? | ||

| 27, 28, 30, 55 | NC | Not Used | Not Used | Not Used | Not Used | Not Used | Not Used | pins unused / Not Connected |

Structure[edit | edit source]

Only a single 16MB NOR flash chip is used. The 128N is JEDEC CFI compliant and organized as 8,388,608 words or 16,777,216 bytes, addressable as 16-bit words (PS3 modus operandi) and 8-bit / 1 byte when the BYTE# signal is logic zero.

| ||||||||||||||||||||||||||||||||||||||